MICRO ELECTRONIC AND MECHANICAL SYSTEMS

# MICRO ELECTRONIC AND MECHANICAL SYSTEMS

Edited by Kenichi Takahata

I-Tech

Published by In-Teh

#### In-Teh

Olajnica 19/2, 32000 Vukovar, Croatia

Abstracting and non-profit use of the material is permitted with credit to the source. Statements and opinions expressed in the chapters are these of the individual contributors and not necessarily those of the editors or publisher. No responsibility is accepted for the accuracy of information contained in the published articles. Publisher assumes no responsibility liability for any damage or injury to persons or property arising out of the use of any materials, instructions, methods or ideas contained inside. After this work has been published by the In-Teh, authors have the right to republish it, in whole or part, in any publication of which they are an author or editor, and the make other personal use of the work.

© 2009 In-teh www.in-teh.org Additional copies can be obtained from: publication@intechweb.org

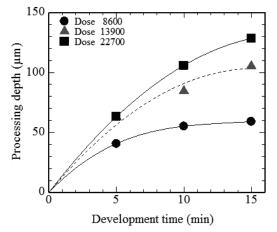

First published December 2009 Printed in India

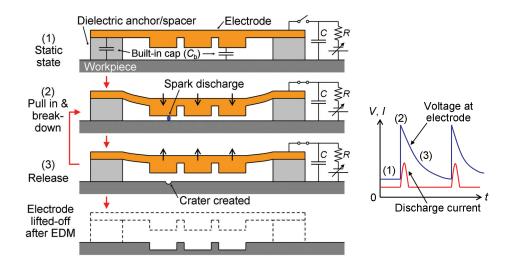

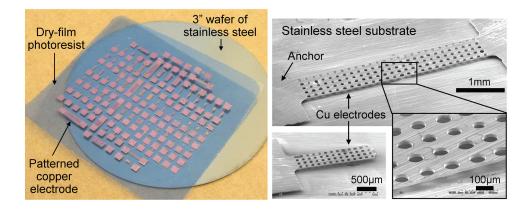

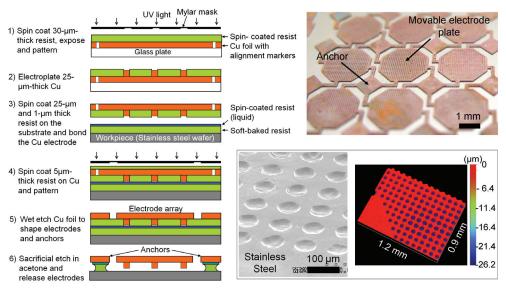

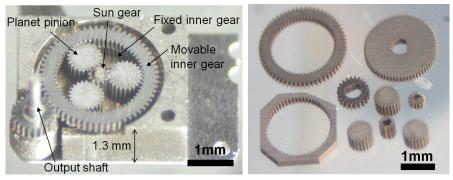

Technical Editor: Teodora Smiljanic

Micro Electronic and Mechanical Systems, Edited by Kenichi Takahata p. cm. ISBN 978-953-307-027-8

# Preface

The miniaturization and performance improvement in semiconductor devices and integrated circuits (ICs) are expected to continue through leveraging of nanotechnologies and nanomaterials. This evolution should accelerate the System-on-a-Chip (SoC) trend, i.e., singlechip integration of multifunctional, mixed-signal electronic components, toward realizing embedded nanoelectronic systems. In parallel with advances in electronics, we are witnessing the rise of micro-electro-mechanical systems (MEMS), with rapidly growing commercial opportunities and markets extending to a broader range of industrial sectors on a global scale.

The emergence of MEMS is primarily attributed to the establishment of sophisticated IC manufacturing techniques and processes that served as a foundation for realizing many innovative silicon-based micromachining technologies. Advances in this area have brought about a revolution in mechanical engineering, enabling the miniaturization and system-level integration of mechanical structures and devices with ICs on a chip for MEMS fabrication. With miniaturized sensors and actuators, MEMS provide us with the ability to interact with micro-scale environments with non-electrical/-electronic parameters, found in the mechanical, optical, chemical, biological, and other domains. This exceptional ability has led to their application in fields ranging from implantable medical sensors to video game controllers. There is no doubt that continued development of MEMS and microsystems with electromechanical functionalities will extend their contribution to society, in parallel with the evolution of IC technologies.

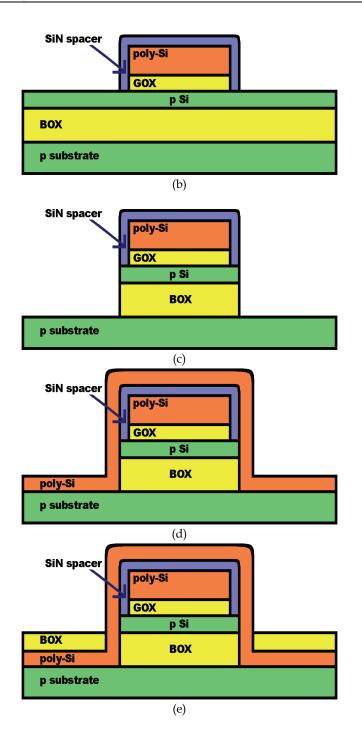

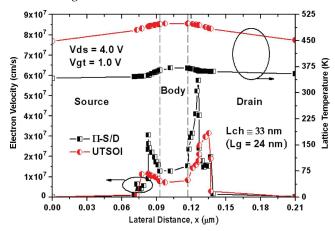

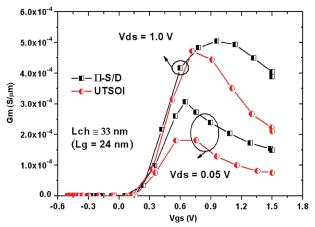

This book discusses key aspects of these technology areas, organized in twenty-seven chapters that present the latest research developments in micro electronic and mechanical systems. The book addresses a wide range of fundamental and practical issues related to MEMS, advanced metal-oxide-semiconductor (MOS) and complementary MOS (CMOS) devices, SoC technology, integrated circuit testing and verification, and other important topics in the field. Several chapters cover state-of-the-art microfabrication techniques and materials as enabling technologies for the microsystems. Reliability issues concerning both electronic and mechanical aspects of these devices and systems are also addressed in various chapters.

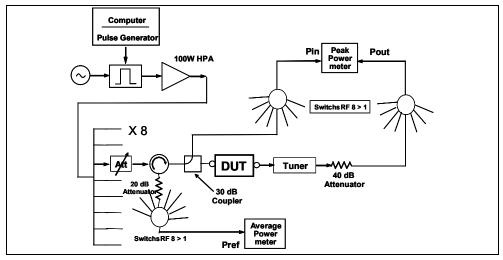

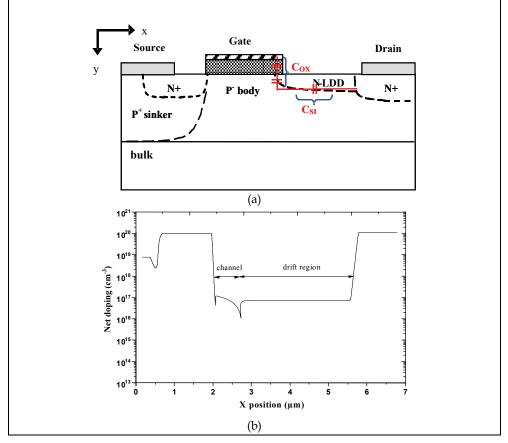

This book is the result of contributions from many researchers worldwide. I would like to thank the authors for their kind cooperation and efforts to provide their most up-to-date research results. A special thanks goes to the IN-TECH team for their dedicated work in making this book possible.

November 2009

Editor

**Kenichi Takahata** Canada Research Chair University of British Columbia, Vancouver, Canada

# Contents

|    | Preface                                                                                                                                                                                                                                                           | V   |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

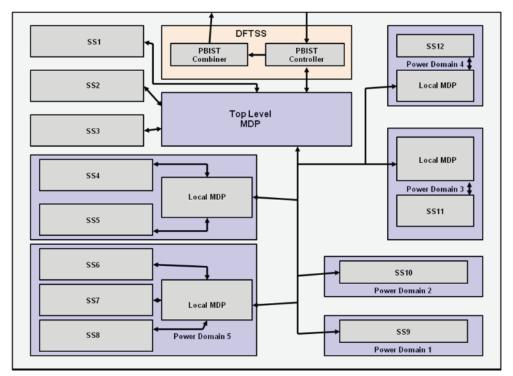

| 1. | Membrane Micro Emboss (MeME) Process<br>for 3-D Membrane Microdevice<br>Masashi Ikeuchi and Koji Ikuta                                                                                                                                                            | 001 |

| 2. | A Review of Thermoelectric MEMS Devices for Micro-power<br>Generation, Heating and Cooling Applications<br><i>Chris Gould and Noel Shammas</i>                                                                                                                    | 015 |

| 3. | Micro Power Generation from Micro Fuel Cell Combined<br>with Micro Methanol Reformer<br><i>Taegyu Kim</i>                                                                                                                                                         | 025 |

| 4. | Non-contact Measurement of Thickness Uniformity of Chemically<br>Etched Si Membranes by Fiber-Optic Low-Coherence Interferometry<br>Zoran Djinovic, Milos Tomic, Lazo Manojlovic,<br>Zarko Lazic and Milce Smiljanic                                              | 051 |

| 5. | Nanomembrane: A New MEMS/NEMS Building Block<br>Jovan Matovic and Zoran Jakšić                                                                                                                                                                                    | 061 |

| 6. | Nanomembrane-Enabled MEMS Sensors:<br>Case of Plasmonic Devices for Chemical and Biological Sensing<br>Zoran Jakšić and Jovan Matovic                                                                                                                             | 085 |

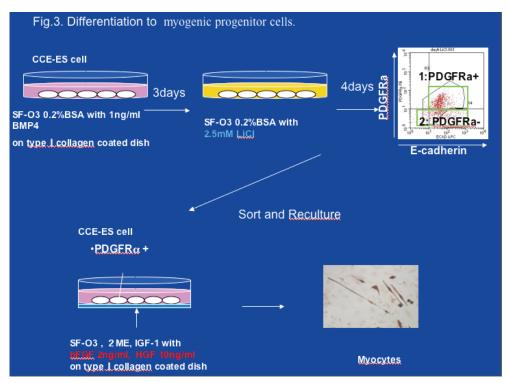

| 7. | Specific Serum-free Conditions can Differentiate<br>Mouse Embryonic Stem Cells into Osteochondrogenic<br>and Myogenic Progenitors.<br><i>Hidetoshi Sakurai, Yuta Inami, Naomi Nishio, Sachiko Ito,</i><br><i>Toru Yosikai, Haruhiko Suzuki and Ken-Ichi Isobe</i> | 107 |

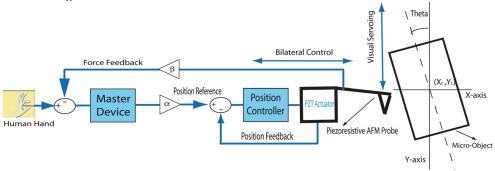

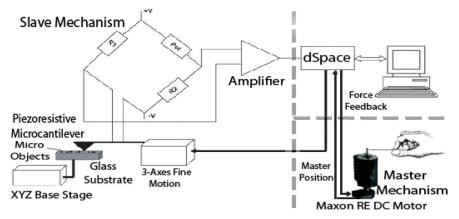

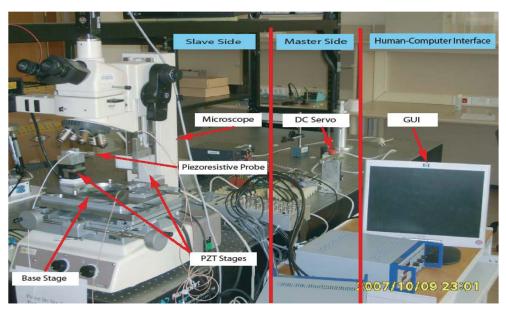

| 8. | Micromanipulation with Haptic Interface<br>Shahzad Khan, Hans H. Langen and Asif Sabanovic                                                                                                                                                                        | 113 |

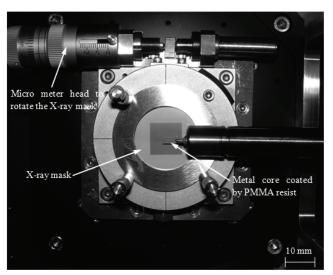

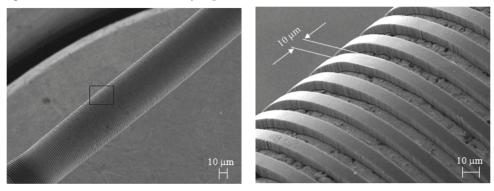

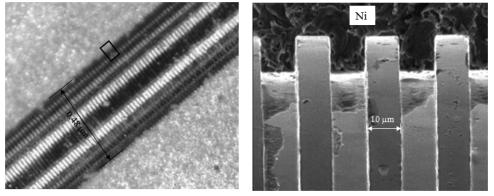

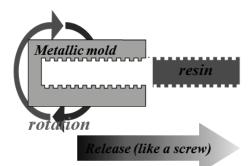

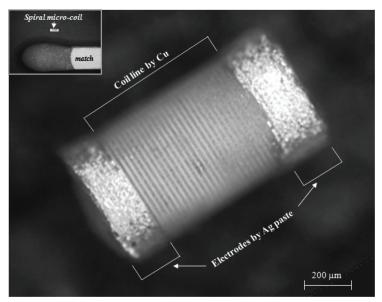

| 9. | Fabrication of High Aspect Ratio Microcoils<br>for Electromagnetic Actuators<br>Daiji Noda, Masaru Setomoto and Tadashi Hattori                                                                                                                                   | 125 |

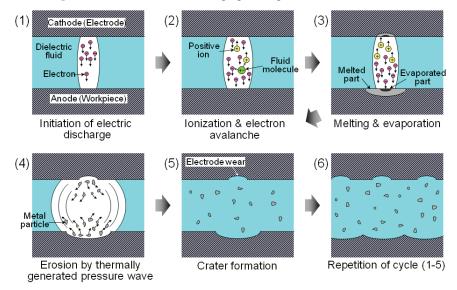

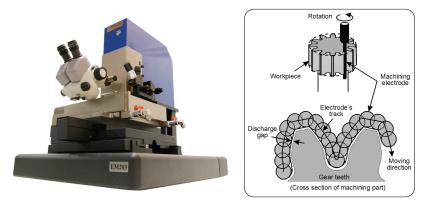

| 10. | Micro-Electro-Discharge Machining Technologies for MEMS<br>Kenichi Takahata                                                                                                                                                                         | 143 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11. | Mechanical Properties of MEMS Materials<br>Zdravko Stanimirović and Ivanka Stanimirović                                                                                                                                                             | 165 |

| 12. | Reliability of MEMS<br>Ivanka Stanimirović and Zdravko Stanimirović                                                                                                                                                                                 | 177 |

| 13. | Numerical Simulation of Plasma-Chemical Processing Semiconductors<br>Yurii N. Grigoryev and Aleksey G. Gorobchuk                                                                                                                                    | 185 |

| 14. | Experimental Studies on Doped and Co-Doped ZnO<br>Thin Films Prepared by RF Diode Sputtering<br><i>Krasimira Shtereva, Vladimir Tvarozek, Pavel Sutta,</i><br><i>Jaroslav Kovac and Ivan Novotny</i>                                                | 211 |

| 15. | Self-Aligned π-Shaped Source/Drain Ultrathin SOI MOSFETs<br>Yi-Chuen Eng and Jyi-Tsong Lin                                                                                                                                                          | 235 |

| 16. | Accurate LDMOS Model Extraction using DC, CV and Small Signal<br>S Parameters Measurements for Reliability Issues<br>Mouna Chetibi-Riah, Mohamed Masmoudi, Hichame Maanane,<br>Jérôme Marcon, Karine Mourgues, Mohamed Ketata and Philippe Eudeline | 245 |

| 17. | Comparative Analysis of High Frequency Characteristics<br>of DDR and DAR IMPATT Diodes<br><i>Alexander Zemliak</i>                                                                                                                                  | 267 |

| 18. | Ohmic Contacts for High Power and High Temperature Microelectronics<br>Lilyana Kolaklieva and Roumen Kakanakov                                                                                                                                      | 293 |

| 19. | Implications of Negative Bias Temperature Instability<br>in Power MOS Transistors<br>Danijel Danković, Ivica Manić, Snežana Djorić-Veljković, Vojkan Davidović,<br>Snežana Golubović and Ninoslav Stojadinović                                      | 319 |

| 20. | Radiation Hardness of Semiconductor Programmable Memories<br>and Over-voltage Protection Components<br>Boris Lončar, Miloš Vujisić, Koviljka Stanković and Predrag Osmokrović                                                                       | 343 |

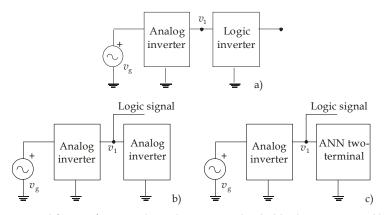

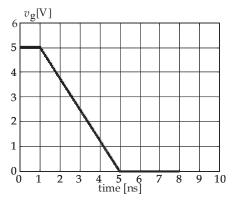

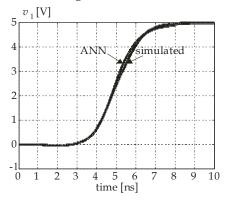

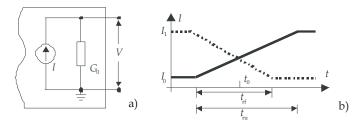

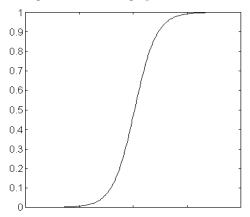

| 21. | ANN Application to Modelling of the D/A and A/D Interface for Mixed-<br>mode Behavioural Simulation<br><i>Miona Andrejević Stošović and Vančo Litovski</i>                                                                                          | 369 |

| 22. | Electronic Circuits Diagnosis using Artificial Neural Networks<br>Miona Andrejević Stošović and Vančo Litovski                                                                                                                                      | 385 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 23. | Integration Verification in System on Chips Using Formal Techniques Subir K Roy                                                                                                                                                                     | 405 |

| 24. | Test Generation based on CLP<br>Giuseppe Di Guglielmo, Franco Fummi,<br>Cristina Marconcini and Graziano Pravadelli                                                                                                                                 | 431 |

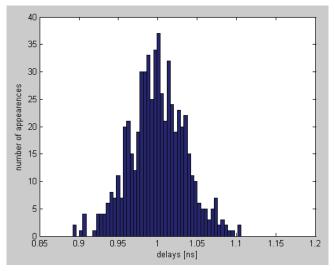

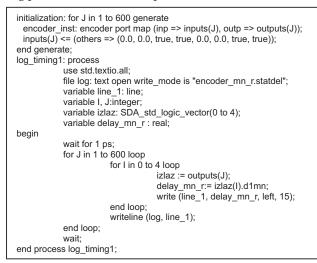

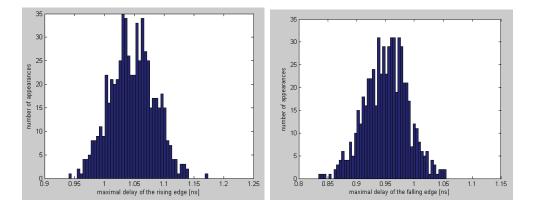

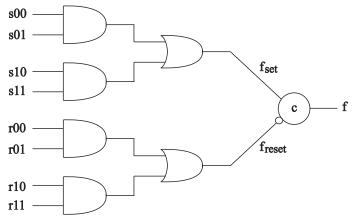

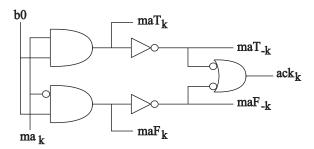

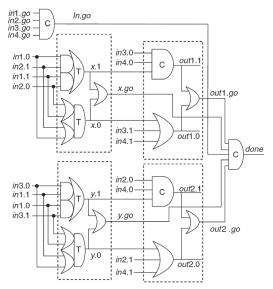

| 25. | New Concepts of Asynchronous Circuits<br>Worst-case Delay and Yield Estimation<br><i>Miljana Milić and Vančo Litovski</i>                                                                                                                           | 455 |

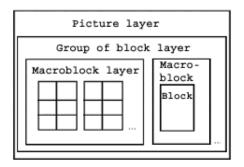

| 26. | Neuron Network Applied to Video Encoder<br>Branko Markoski, Jovan etrajčić, Jasna Mihailović, Branko Petrevski,<br>Miroslava Petrevski, Borislav Obradović, Zoran Milošević,<br>Zdravko Ivanković, Dobrivoje Martinov and Dušanka Tesanović         | 477 |

| 27. | Single Photon Eigen-Problem with Complex Internal Dynamics<br>Nenad V. Delić, Jovan P. Šetrajčić, Dragoljub Lj. Mirjanić,<br>Zdravko Ivanković, Dobrivoje Martinov, Snežana Jokić,<br>Ivana Petrevska–Đukić, Dušanka Tešanović and Svetlana Pelemiš | 493 |

# Membrane Micro Emboss (MeME) Process for 3-D Membrane Microdevice

Masashi Ikeuchi and Koji Ikuta

Graduate School of Engineering, Nagoya University Japan

## 1. Introduction

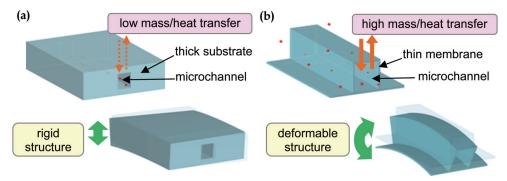

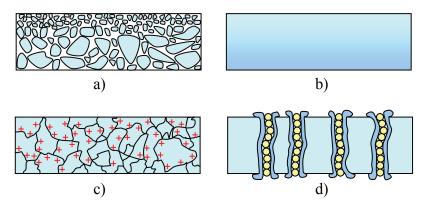

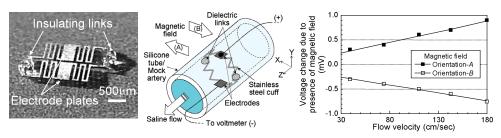

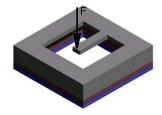

Recent advances in micro- and nanofabrication technologies have enabled the development of miniaturized accelerometers, gyroscopes, µTAS chips, etc. These microdevices are made of substrates having thicknesses relatively greater (~100µm) than the feature scale of the microfabricated components (1~10 µm, Fig.1a). Conversely, the microscale organelles or tissues of natural creatures are made of substrates, or membranes, that are relatively thin compared to their feature size. For example, a human blood capillary, which is  $10\sim100 \ \mu m$ in diameter, has vessel walls with thicknesses of  $\sim 1 \,\mu$ m. To give another example, a cell with a diameter of ~10 µm is composed of lipid bilayer membranes with thicknesses of ~10 nm. This fundamental characteristic of the architecture of biological microstructures, which is totally different from that of artificial microdevices, makes life a highly adaptable system from both chemical and physical perspectives. The small thickness of the membrane enhances transport of heat and substances between the body and its surroundings, and it provides softness to the body, enabling passive and active morphological changes for adapting to the environment. These characteristics of biological microstructures should greatly encourage us to develop new types of MEMS and µTAS devices. However, in reality, little research has been conducted on the development of 3-D microdevices composed of thin membranes, which we call "3-D membrane microdevices" (Fig.1b).

Fig. 1. Schematics of (a) conventional "bulk" microdevice and (b) "3-D membrane microdevice"

The purpose of this chapter is to introduce the concept of 3-D membrane microdevices and highlight some advances being made in our laboratory. The chapter starts with a section describing a novel microfabrication technique, namely, the membrane micro emboss (MeME) process, which was developed to realize 3-D membrane microstructures. In the following sections, several applications of 3-D membrane microdevices in  $\mu$ TAS and MEMS fields are presented. First, a microfluidic device composed of thin porous biodegradable membranes is described. This device was developed for tissue engineering purposes. Next, a novel micropneumatic actuator composed of folded 3-D membrane chambers is described. The actuator was intended for use as a microactive catheter for safer intravascular treatment. Finally, we conclude the chapter and present our perspectives on 3-D membrane microdevices.

## 2. Membrane Micro Emboss (MeME) process

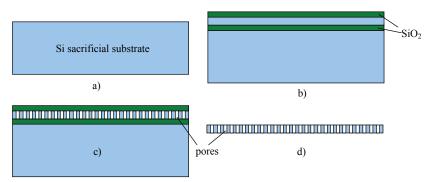

Various micro fabrication processes can be used to fabricate MEMS or  $\mu$ TAS devices. However, few processes are useful for the fabrication of 3-D membrane microstructure, especially for polymer materials. Among conventional microfabrication processes, the chemical vapor deposition (CVD) process using parylene and the microthermoforming process can be employed. Although the CVD process using parylene is used to fabricate 3-D membrane microstructures (Zhenga et al., 2007; Liua et al., 2008), the limitations caused by the unavailability of suitable materials and low production rates present significant problems. The microthermoforming process (Truckenmüller et al., 2002; Giselbrecht et al., 2006) can be applied to a wide variety of thermoplastic materials and is suitable for mass production; however, it cannot be applied to highly porous membranes because the pressurized fluid leaks through the pores.

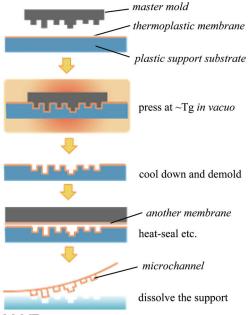

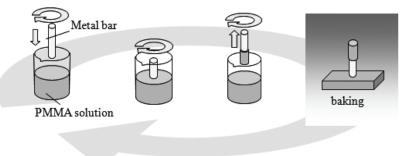

Fig. 2. Flowchart of the MeME process

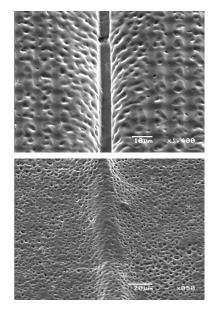

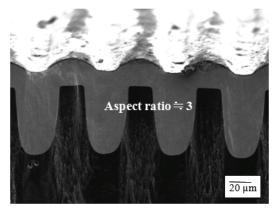

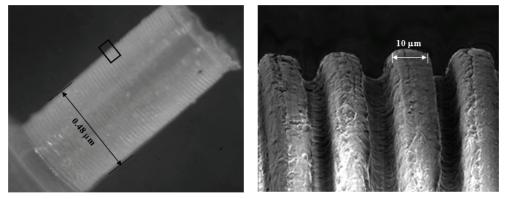

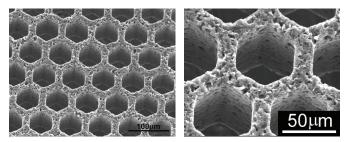

The MeME process (Fig.2) was developed to realize 3-D membrane microstructures from a wide variety of materials including porous materials (Ikeuchi & Ikuta, 2005; Ikeuchi & Ikuta, 2006, a). This process needs a master mold, a thermoplastic polymer membrane, and a deformable plastic support substrate. First, the polymer membrane is set between the master mold and the support substrate. Then, this assemblage is heated to temperatures around the glass transition point (Tg) of the polymer membrane. Next, the master mold is pressurized against the membrane *in vacuo*. During pressurization, the membrane is deformed along with the support substrate to match the surface of the master mold. After cooling to the initial temperature, the master mold is separated from the deformed membrane. To fabricate sealed microchannels, another planar membrane is placed on the deformed membrane and sealed using heat-sealing, solvent gas bonding, or other sealing techniques. The fabrication of the membrane microfluidic device is completed by dissolving the support substrate in a selective solvent. The process is applicable to various materials, since it only requires the membrane material to be thermoplastic. When polylactic acid (PLA) (Tg, 57°C; thickness, 5  $\mu$ m) was used as a membrane material and paraffin (melting point, 70 °C) was used as a support substrate, the lateral and vertical resolutions of the process were at least 10 µm and 5 µm, respectively (Fig. 3) (Ikeuchi & Ikuta, 2006, a). The resolutions can be further improved by using thinner membranes and harder support substrates.

In the following two sections, several applications of the MeME process are described.

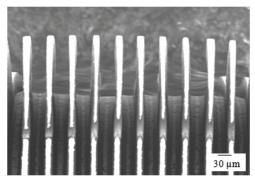

Fig. 3. SEM images of the topside (upper) and backside (lower) of the deformed porous PLA membrane.

# 3. Membrane microfluidic device for tissue engineering

#### 3.1 Background

Throughout the history of biology, cell culture has been carried out on planar glass or in polymer dishes. The cells cultured on a planar substrate proliferate laterally to form a thin

layer of cells. Biologists have studied cellular dynamics using these two-dimensional cellular constructs. In the natural environment, however, cells proliferate three-dimensionally, and thus, show behaviours and functions different from those of cells in 2-D *in vitro* cultures.

Recently, cell culture in 3-D conditions has attracted considerable attention for studying natural cell behaviours and, from a more practical perspective, for regenerating fully functional large tissues and organs for transplantation. Some biologists culture cells under 3-D conditions by using soft hydrogel materials (collagen, MatrigeI<sup>TM</sup>, etc.) or stacking cell sheets (Liu & Bhatia, 2002; Bryant & Anseth, 2002; Sekiya et al., 2006.). There is a big difference, however, between artificial 3-D conditions and *in vivo* conditions because of the thickness of the cultured cellular constructs. Thick tissues *in vivo* can survive on nutrients supplied from surrounding blood capillary networks. In contrast, we can stack only a few layers of cells *in vitro* due to limitations with regard to the diffusion distance of nutrients, which can be supplied only through the outer surface of the construct.

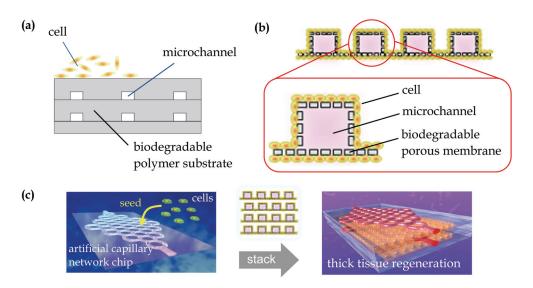

To solve this problem, King et al. (2004.) attempted to construct microfluidic chips made of biodegradable polymers. They fabricated microchannels in biodegradable polymer substrates using  $\mu$ TAS or lab-on-chip technologies, and they cultured cells on the chip by supplying the culture medium through microchannels (Fig. 4a). They were unable to culture thick tissues, however, because the cells cultured on the chip tended to be distributed at a low density with poor homogeneity. These problems arise due to the thickness of the chip. Cells seeded on the thick microchannel chips proliferate on the surface of the chip rather than growing within the chip substrate.

In this section, we describe the MeME process as applied to fabricate 3-D thin membrane microstructure, which solves the problems associated with conventional methods for tissue engineering.

### 3.2 Artificial capillary network chip

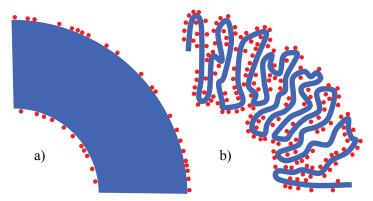

To realize both the nutrients supply and homogeneous cell distribution in 3-D constructs, we propose the artificial capillary network chip as a novel 3-D cell culture device (Fig. 4b). This chip has a microchannel network made of a thin biocompatible polymer membrane with penetrating micropores.

Cells seeded on this chip with soft hydrogel materials, or cells stacked on this chip as cell sheets, can maintain a thick 3-D construct because of nutrients supplied from the porous microchannel network. Unlike the thick conventional microchannel chip, the membrane composing the microchannel wall is thin enough for cells to distribute homogeneously in the 3-D constructs. Biodegradable polymers can be used, instead of conventional polymers, as the membrane material to regenerate tissues for transplantation. Larger tissues can be fabricated by stacking these chips (Fig. 4c).

A prototype of the chip with highly branched microchannels was fabricated from a porous PLA membrane. The porous PLA membrane was formed by spin-coating following phase separation technique (Ikeuchi & Ikuta, 2006, b). The diameter and density of the pores can be controlled independently by adjusting the water content and PLA content of the coating solution, respectively. Here, the pore diameter was adjusted to  $\phi \sim 1 \mu m$  to prevent the cells ( $\phi \sim 5 \mu m$ ) from entering the microchannel, and the thickness was adjusted to 5  $\mu m$ .

The master mold was made by microstereolithography developed in our laboratory (Ikuta & Hirowatari, 1993). The surface of the mold was coated with a fluorocarbon polymer for easy

Fig. 4. (a) Schematic cross-section of the conventional microchannel chip for cell culture. (b) Schematic cross-section of artificial capillary network chip. (c) Conceptual scheme of *in vitro* 3-D thick tissue regeneration using artificial capillary network chip

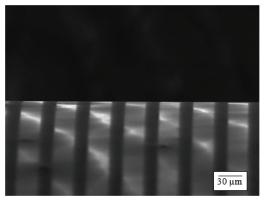

removal of the mold. The master mold was pressurized onto the membrane at  $0.5 \,\mu$ m/s for 500 s. at 55°C *in vacuo*. After cooling to 25°C, the mold was removed. The embossed membrane was heat-sealed with another membrane of the same material at 70°C for 30 s. A red solution was filled into the microchannels by capillary force. No leaking or blockage of the microchannel was observed (Fig. 5a). Figs. 5b and c show the topside and the backside of a microchannel in the prototype chip before sealing, respectively. Most of the micropores can be preserved on both sides of the microchannel wall even after the MeME process by fine tuning the process parameters (speed, temperature, and material of support substrate).

#### 3.3 Validation of the chip

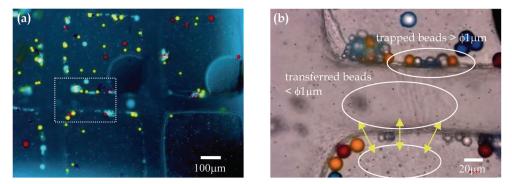

To check the size-selective permeability of the microchannel wall of the chip, a suspension of microbeads with diameters varying from  $\phi$ 100 nm to  $\phi$ 15  $\mu$ m was poured on the chip (Fig. 6a). Beads smaller than  $\phi$ 1  $\mu$ m penetrated the wall but larger beads were trapped on the wall (Fig. 6b). This result means that nutrients and gases flowing through the microchannels can diffuse out into the cellular constructs on the chip, while at the same time, the microchannel walls support the thick 3-D cellular constructs.

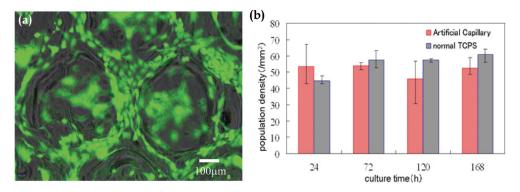

The biocompatibility of the chip was also tested by culturing human endothelial cells (HUVEC) using another prototype chip. Fig. 7a shows a fluorescent image of the cells on the chip after culturing for 120 h. The cells spread as usual and showed no damage. The time course of the cell density on the chip was also equivalent to that for conventional tissue culture polystyrene flasks (Fig. 7b). These results prove that the chip was biocompatible with HUVEC. The success of HUVEC culture on the microchannel offers interesting possibilities for co-culture with other parenchyma cells to fabricate functional tissues.

Fig. 5. A prototype chip made of a porous PLA membrane. (a) Optical microscopy image. (b, c) SEM images of the topside and the backside of the chip, respectively.

Fig. 6. (a) Fluorescent microscopy image of the chip after pouring a microbead suspension (b) Magnified view of the white-rectangle area in (a).

Fig. 7. HUVEC culture on the chip. (a) Fluorescent view of the cell on the chip after 120 h. (b) Transition of cell population density with culture time.

#### 3.4 Summary

In this section, the artificial capillary network chip with a 3-D membrane microstructure was proposed and its development from the viewpoint of realizing thick 3-D tissue culture *in vitro* was described. Prototype chips were successfully fabricated using the MeME process, and their size-selective permeability and biocompatibility were verified. This chip could potentially become a key technology in the study of cellular dynamics under 3-D conditions; moreover, it could be used to regenerate large tissues or organs for transplantation in the near future.

# 4. Pressure-driven microactive catheter

#### 4.1 Background

Recently, catheterization has been widely applied in intravascular surgery as an alternative to conventional surgical techniques, which are highly invasive. In catheterization, a thin flexible tube called a catheter is inserted into a blood vessel from the leg or arm. The catheter can be advanced into the patient's heart or brain for treatment or inspection. The operation leaves just a tiny puncture on the arm or leg where the catheter has been inserted, and therefore, causes less damage and fewer scars on the patient than conventional open surgery.

A major problem with catheterization, however, is the difficulty of manipulation in narrow and branched blood vessels. Since conventional catheters have no active bending capability at the tip, the doctor can control the direction of the tip only by pushing and rotating the catheter at the inlet which is far away from the tip. Thus, catheterization in narrow and complicated blood vessels is extremely difficult.

To solve this problem, several types of active catheters have been proposed (Mineta et al., 2002; Ikuta et al., 2003; Fang et al., 2007). They are classified into two types depending on the bending mechanism. The first type consists of electrically driven active catheters. These catheters have actuators that use shape memory alloys or polymer gels at the tip and can be bent from outside the body by applying a current to the actuators. Even though electrical actuators are suitable for miniaturization, the use of electricity inside the heart or brain

poses the risk of fatal damage due to microshock or heat in the case of an accident (Manecke et al., 2002; Bunch et al., 2005).

The second type consists of a pressure-driven active catheter, as proposed by Ikuta et al. (2003). It has a hollow bellows made of soft silicone rubber at the tip, and the tip can be bent by supplying saline water into the bellows through a tube connected to the bellows. Since no electricity is necessary for actuation, it is superior in safety compared to electrically driven active catheters. In addition, it can be applied to MRI monitoring, which is a fundamental tool in catheterization, because no metal parts are used in this catheter. In spite of its superiority, the minimum size of this type of catheter that can be attained with conventional injection molding processes using a pair of a male and a female mold is  $\phi \sim 1$  mm, whereas the catheter must be smaller than  $\phi \sim 300 \ \mu m$  for complex intravascular surgery. This limitation arises due to the difficulties involved in 3-D fabrication of a pair of male and female molds with micrometer accuracy.

Although a pressure-driven balloon-type microactuator made from a polydimethylsiloxane (PDMS) molding technique was reported for use in MEMS applications (Konishi et al., 2006), it cannot be applied to catheterization due to the risk of damage to blood vessels caused by large expansion of the actuator during bending. In short, there is no process available to fabricate microscale pressure-driven active catheters.

In this section, we describe how the MeME process can be combined with an excimer laser ablation technique to realize a pressure-driven microactive catheter with a 3-D thin membrane microstructure.

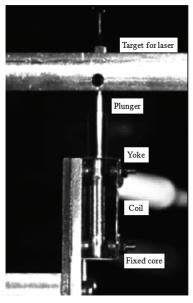

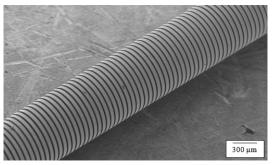

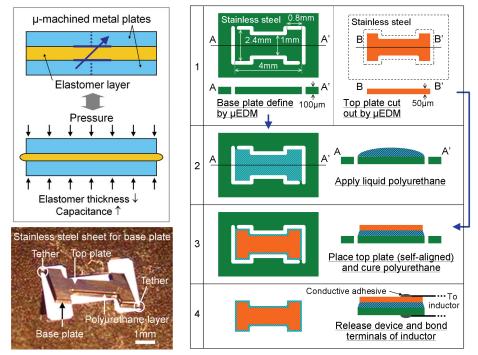

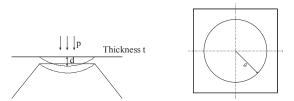

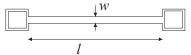

#### 4.2 Bellows composed of folded membrane microchambers

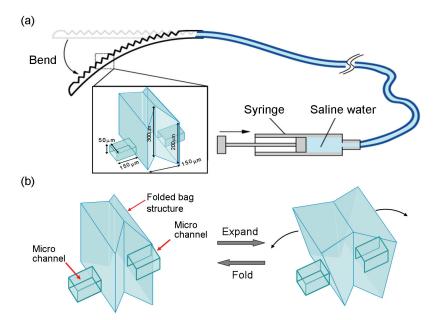

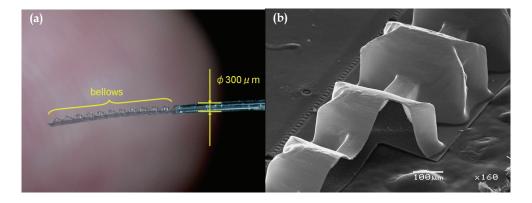

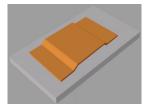

We designed a pressure-driven microactive catheter composed of hollow bellows; the catheter was made of a biocompatible polymer membrane (thickness, 5  $\mu$ m), a motorized syringe, and a Teflon microtube (Fig. 8a). A pressure gauge was attached to the microtube at the base to monitor the pressure and provide the pressure value as feedback to the motorized syringe. The diameter of the catheter was set at  $\phi$  300  $\mu$ m, because that is the minimum size used in clinical practice.

The bellows are composed of a series of folded microchambers and microchannels connecting the chambers. Since the bottom of each folded chamber is fixed to another membrane, only the upper part of the chamber can be expanded by increasing the inner pressure of the chamber (Fig. 8b). Thus, the bellows in their entirety can be bent in one direction by supplying saline water from the syringe through the microtube, because only one side of the bellows extends. Furthermore, the alternating arrangement of microchannels and microchambers prevents the bellows from expanding in diameter during bending, since the microchannels work as rigid frames to connect the topside and backside membranes of the bellows.

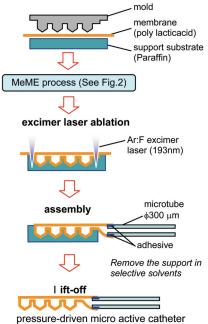

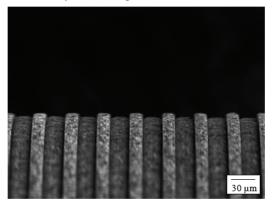

The catheter was fabricated using the membrane micro emboss following excimer laser ablation (MeME-X) process (Fig. 9) (Ikeuchi & Ikuta, 2008). In the MeME-X process, at first, the hollow microbellows were formed from PLA membranes (thickness, 5  $\mu$ m) using the MeME process. By using excimer laser ablation (ArF, 193 nm), the outline of the bellows was cut out from the sealed membranes, and an opening was made at one end. After the bellows were connected to a microtube by an adhesive under an optical microscope, the

Fig. 8. (a) Schematic of the pressure-driven microactive catheter system with bendable bellows made of a thin membrane at the tip (b) Bending of the bellows through expansion of each folded microchamber

Fig. 9. Flowchart of the MeME-X process

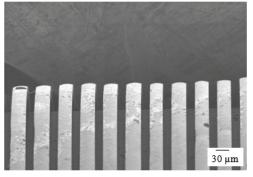

support substrate was selectively dissolved by immersion in hexane. Finally, the catheter was successfully fabricated (Fig. 10a). The entire process was completed in 10–15min. To show the cross-section of the hollow bellows, the bellows were cut in the middle using the excimer laser. The bellows composed of a series of folded microchambers and microchannels were precisely fabricated on both the outside and the inside, and the thin membrane was uniformly deformed to yield a hollow microstructure (Fig. 10b).

Fig. 10. (a) Completed pressure-driven micro active catheter  $\phi$  300 µm. (b) SEM image of the bellows cut at the middle to show the cross-section and the inner structure.

#### 4.3 Validation of the catheter

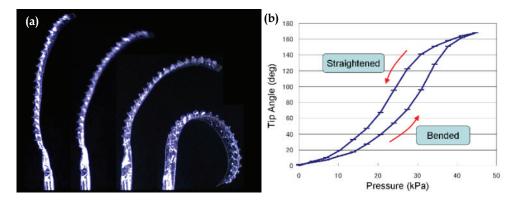

The bellows were bent at an arbitrary angle between 0° and 180° through water pressure applied by a motorized syringe (Fig. 11a). The range of the bending angle is sufficient for intravascular operation, and it can be extended by increasing the folding angle of each microchamber of the bellows or by increasing the number of microchambers, if necessary.

Fig. 11. (a) Bending demonstration of the pressure-driven micro active catheter from 0 to 180 degrees. (b) Relation between applied pressure (P) and bending angle ( $\theta$ ) of the tip

The hysteresis of the P- $\theta$  curve is apparently caused by the buckling behavior of the folded chambers and air trapped in the microtube (Fig. 11b). The buckling behavior can be improved by modifying the folding angle and pattern of the chambers, and the trapping of air in the system can be prevented by assembling the catheter *in vacuo*. Most importantly, little increase in the diameter of the bellows was observed during bending due to the microchannels inserted between the microchambers. This leads to a safer and smoother insertion of the catheter at bifurcations.

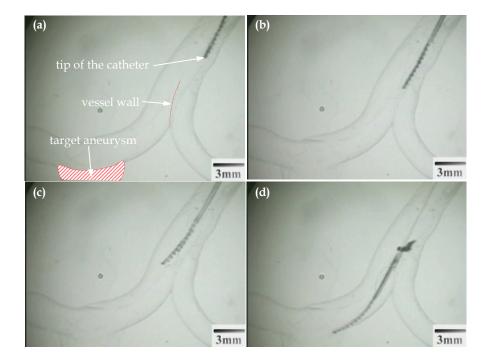

For *in vitro* demonstration of the active catheter, a small blood vessel model made of silicone was fabricated using the lost-wax method. The model consists of narrow blood vessels of  $\phi$  1 ~ 3 mm into which conventional active catheters could not be inserted. The pressure-driven microactive catheter was actuated and inserted into the narrow vessels (Fig. 12a). At the bifurcation, the catheter was bent slightly to the left from the straight position (Fig. 12b,c) by supplying saline water from the syringe, turned to the desired direction, and then successfully introduced into the target aneurysm (Fig.12d).

Fig. 12. Video frames showing insertion of the catheter into a 3-D vascular model

#### 4.4 Summary

In this section, the pressure-driven microactive catheter was proposed and its development by the MeME-X process was described. The pressure-driven microactive catheter, with its extremely small size and high safety, should promote the application of catheterization in complex intravascular surgery, which is at present not possible with conventional surgical tools. For further improvements, microchannels for drug delivery and/or blood sampling could be attached to the bellows. This can be achieved by simply adding microchannel templates on the master mold of the bellows. Furthermore, the nonelectrical actuation mechanism of this catheter, which has a 3-D membrane microstructure, can be widely extended to safe medical tools and microactuators in the microrobotics field.

## 5. Conclusions and perspectives

In this chapter, the concept of 3-D membrane microdevices was introduced and the development of the MeME process was described. To utilize its characteristics, the concept was applied to actual devices in two different fields. First, focusing on the efficient transfer of substances and heat in 3-D membrane microchannels, an artificial capillary network chip was developed for tissue engineering purposes. Second, utilizing the high elastic deformability of 3-D membrane microstructures, hollow bellows composed of folded microchambers and microchannels were developed to realize a pressure-driven microactive catheter.

Biological organisms are fundamentally characterized by a 3-D membrane microstructure. From intracellular organelles to vascular networks, from plant leaves to insect wings, the exquisite architectures prevalent in nature greatly inspires us to develop novel micro/nanodevices. The study of 3-D membrane microdevices has just emerged out of the proof-of-concept stage. To further expand the scope of applications of 3-D membrane microdevices, our laboratory is actively engaged in the exploration of a variety of materials applicable to the MeME process and improvement of the resolutions of the MeME process toward the nanometer scale. With its unique advantages, the 3-D membrane microdevice technology should contribute to drug delivery, tissue engineering, electric power generation, smart skin development and many other fields in the near future.

# 6. References

- Bryant, S. & Anseth, K. (2002). Hydrogel properties influence ECM production by chondrocytes photoencapsulated in poly(ethylene glycol) hydrogels. *Journal of Biomedical Materials Research*, Vol. 59, Issue 1, 63-72.

- Bunch, T.J., Bruce, G.K., Mahapatra S., Johnson S.B., Miller D.V., Sarabanda A.V., Milton M.A. & Packer D.L. (2005). Mechanisms of phrenic nerve injury during radiofrequency ablation at the pulmonary vein orifice. *Journal of Cardiovascular Electrophysiology*, Vol. 16, Issue 12, 1318-1325.

- Fang, B.K., Ju, M.S. & Lin, C.C.K. (2007). A new approach to develop ionic polymer-metal composites (IPMC) actuator: Fabrication and control for active catheter systems. *Sensors and Actuators A*, Vol. 137, Issue 2, 321-329

- Giselbrecht, S., Gietzelt, T., Gottwald, E., Trautmann, C., Truckenmüller, R., Weibezahn, K.F. & Welle, A. (2006). 3D tissue culture substrates produced by microthermoforming of pre-processed polymer films. *Biomedical Microdevices*, Vol. 8, Issue 3, 191-199.

- Ikeuchi, M. & Ikuta, K. (2005), Fabrication of biodegradable membrane micro-channels for artificial blood capillary networks using membrane micro embossing (MeME). *Transactions of JSMBE*. Vol. 43, Issue 4, 646-652

- Ikeuchi, M. & Ikuta, K. (2006,a). The membrane micro emboss (MeME) process for fabricating 3-D microfluidic device formed from thin polymer membrane. *Proc.* μTAS'06, pp. 693-695, ISBN4-9903269-0-3-C3043, Tokyo, Nov. 2006.

- Ikeuchi, M. & Ikuta, K. (2006,b). On-site size-selective particle sampling using mesoporous polymer membrane microfluidic device. *Proc.* μTAS'06, pp. 1169-1171, ISBN4-9903269-0-3-C3043, Tokyo, Nov. 2006.

- Ikeuchi, M. & Ikuta, K. (2008). Membrane micro emboss following excimer laser ablation (MeME-X) process for pressure-driven micro active catheter. *Proc. MEMS'08*, pp. 62-65, ISBN978-1-4244-1792-6, Tucson, Jan. 2008.

- Ikuta, K. & Hirowatari, K. (1993). Real three dimensional micro fabrication using stereo lithography and metal molding. *Proc. MEMS*'93, pp. 42-47, ISBN0-7803-0957-X, Fort Lauderdale, Feb. 1993.

- Ikuta, K., Ichikawa, H., Suzuki, K. & Yamamoto, T. (2003). Safety active catheter with multisegments driven by innovative hydro-pressure micro actuators. *Proc. MEMS'03*, pp. 130-135, ISBN0-7803-7744-3, Kyoto, Jan. 2003.

- King, K., Wang, C., Mofrad, M., Vacanti, J.P. & Borenstein, J. (2004). Biodegradable microfluidics. Advanced Materials, Vol. 16, 2007-2012

- Konishi, S., Nokata, M., Jeong, O.C., Kusuda, S., Sakakibara, T., Kuwayama, M. & Tsutsumi, H. Pneumatic micro hand and miniaturized parallel link robot for micro manipulation robot system, *Proc. ICRA'06*, pp. 1036-1041, ISBN0-7803-9505-0, Orlando, May 2006.

- Liu, V. & Bhatia, S. (2002). Three-dimensional photopatterning of hydrogels containing living cells. *Biomedical Microdevices*, Vol. 4, Issue 4, 257-266.

- Liua, M.C., Hob, D. & Tai, Y.C. (2008). Monolithic fabrication of three-dimensional microfluidic networks for constructing cell culture array with an "integrated combinatorial mixer. *Sensors and Actuators B*, Vol. 129, Issue 2, 826-833

- Manecke, G.R., Brown, J.C. Landau, A.A., Kapelanski, D.P., St. Laurent, C.M. & Auger, W.R. (2002). An unusual case of pulmonary artery catheter malfunction. *Anesthesia Analgesia*, Vol. 95, 302-304.

- Mineta, T., Mitsui, T., Watanabe, Y., Kobayashi, S., Haga, Y. & Esashi, M. (2002). An active guide wire with shape memory alloy bending actuator fabricated by room temperature process. *Sensors and Actuators A*, Vol. 97-98, 632-637

- Sekiya, S., Shimizu, T., Yamato, M., Kikuchi, A. & Okano, T. (2006). Bioengineered cardiac cell sheet grafts have intrinsic angiogenic potential. *Biochemical and Biophysical Research Communications*, Vol. 341, Issue 2, 573-82.

- Truckenmuller, R., Rummler, Z., Schaller, T. & Schomburg, W.K. (2002). Low-cost thermoforming of micro fluidic analysis chips. *Journal of Micromechanics and Microengineering*, Vol. 12, 375–379

Zhenga, J., Webstera, J.R., Mastrangelob, C.H., Ugazc, V.M., Burnsd M.A. & Burkee, D.T. (2007). Integrated plastic microfluidic device for ssDNA separation. *Sensors and Actuators B*, Vol. 125, Issue 1, 343-351

# A Review of Thermoelectric MEMS Devices for Micro-power Generation, Heating and Cooling Applications

Chris Gould and Noel Shammas Staffordshire University UK

## 1. Introduction

Thermoelectric technology can be used to generate a small amount of electrical power, typically in the  $\mu$ W or mW range, if a temperature difference is maintained between two terminals of a thermoelectric module. Alternatively, a thermoelectric module can operate as a heat pump, providing heating or cooling of an object connected to one side of a thermoelectric module if a DC current is applied to the module's input terminals. This chapter reviews the development of microelectromechanical systems (MEMS) based thermoelectric devices suitable for micro-power generation, heating and cooling applications. The chapter begins with a brief overview of thermoelectric modules are introduced, and a review of recent developments in research, commercial development, and typical application of MEMS based micro-thermoelectric devices is made. The chapter draws conclusions on the development and potential application of MEMS based thermoelectric devices suitable for thermoelectric cooling, heating and micro-power generation.

# 2. Overview of thermoelectric technology, module construction and operation

### 2.1 Overview of thermoelectric technology

Thermoelectricity utilises the Seebeck, Peltier and Thomson effects that were first observed between 1821 and 1851 (Nolas et al, 2001). Practical thermoelectric devices emerged in the 1960's and have developed significantly since then with a number of manufacturers now marketing thermoelectric modules for cooling, heating and power generation applications. Thermoelectric cooling and heating influenced predominantly by the Seebeck effect, with thermoelectric cooling and heating influence although it should always be included in detailed calculations (Rowe, 2006). For power generation applications, a small amount of electrical power, typically in the  $\mu$ W or mW range, can be generated by a thermoelectric module if a temperature difference is maintained between two terminals of a thermoelectric module. Alternatively, a thermoelectric module can operate as a heat pump, providing

heating or cooling of an object connected to one side of a thermoelectric module if a DC current is applied to the module's input terminals. The technology has achieved commercial success in mini-refrigeration, cooling and space-craft power applications, with the consumer market for mini-refrigerators and coolers currently the most successful commercial application (Hachiuma and Fukuda, 2007). Future developments in thermoelectric technology will include the need to reduce the size, and improve the performance, of current thermoelectric devices in order to address thermal problems in microelectronics, and create localised low-power energy sources for electronic systems.

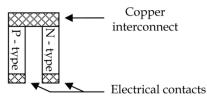

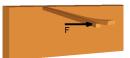

#### 2.2 Standard thermoelectric module construction

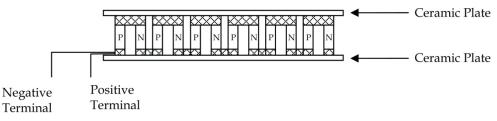

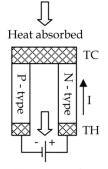

Standard thermoelectric modules are constructed from P-type and N-type thermo-elements, often referred to as thermoelectric couples, connected electrically in series and thermally in parallel. Each couple is constructed from two 'pellets' of semiconductor material usually made from Bismuth Telluride. One of these pellets is doped to create a P-type pellet, the other is doped to produce an N-type pellet. The two pellets are physically linked together on one side, usually with a small strip of copper, and placed between two ceramic plates. The ceramic plates perform two functions; they serve as a foundation on which to mount the thermo-element; and also electrically insulate the thermo-element (Riffat and Ma, 2003). A single couple of a thermoelectric module is shown below in Fig. 1.

Fig. 1. A single couple of a thermoelectric module

The thermo-element, or couple, is then connected electrically in series and thermally in parallel to other couples. Standard thermoelectric modules typically contain a minimum of 3 couples, rising to 127 couples for larger devices. A schematic diagram of a thermoelectric module is shown in Fig. 2.

#### 2.3 Thermoelectric module configuration

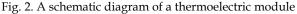

A thermoelectric module can cool or lower the temperature of an object, if the object is attached to the 'cold' side of the module, often referred to as 'TC', and DC electrical power is applied to the module's terminals. Heat from the object will be absorbed by the 'cold' side of the thermoelectric module, and transferred or 'pumped' through to the 'hot' side of the

module 'TH' due to the Peltier effect. Normally, the hot side of the module will be attached to a heat sink in order to reject this heat into the atmosphere. A thermoelectric module operating as a thermoelectric cooler or heat-pump is shown below in Fig. 3. If the polarity of the DC current applied to the thermoelectric module terminals is now reversed, the module will heat the object connected to the cold side of the module, with the other side of the module now cooling down. In this condition, the thermoelectric module is referred to as a thermoelectric heater.

Fig. 3. A thermoelectric module operating as a thermoelectric cooler or heat-pump

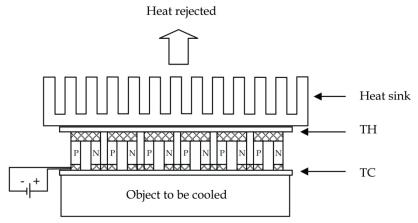

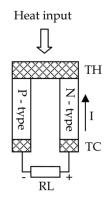

A thermoelectric module can also be used to generate a small amount of electrical power, typically in the  $\mu$ W or mW range, if a temperature difference is maintained between both sides of the module. Normally, one side of the module is attached to a heat source and is referred to as the 'hot' side or 'TH'. The other side of the module is usually attached to a heat sink and is called the 'cold' side or 'TC'. The heat sink is used to create a temperature difference between the cold and hot sides of the module. If a resistive load (RL) is connected across the module's output terminals, electrical power will be generated in the resistive load when a temperature difference exists between the hot and cold sides of the module, due to the Seebeck effect. A thermoelectric module, operating as a thermoelectric power generator, is shown below in Fig. 4.

Fig. 4. A thermoelectric module operating as a thermoelectric power generator

#### 2.4 Operation of standard thermoelectric modules

Semiconductor theory can be used to describe the operation of thermoelectric devices. In Fig. 5, a single thermoelectric couple is connected to operate as a heat pump.

Heat rejected

Fig. 5. A single thermoelectric couple connected as a heat pump

When a DC voltage is applied to the module terminals, electrical current flows from the positive terminal of the supply voltage to the negative terminal. This is shown as an anticlockwise current flow in the configuration shown in Fig. 5. The negative charge carriers, i.e. the electrons, in the n-type bismuth telluride pellet are attracted by the positive pole of the supply voltage, and repelled by the negative potential. Similarly, the positive charge carriers, i.e. the holes, in the p-type material are attracted by the negative potential of the supply voltage, and repelled by the positive potential, and move in an opposite direction to the electron flow. It is these charge carriers that actually transfer the heat from one side of the thermoelectric couple to the other side in the direction of charge carrier movement. In the n-type pellet, the negatively charged electrons are the charge carriers and absorb heat from the 'cold' side of the thermoelectric couple and transfer or 'pump' this heat to the 'hot' side of the couple in a clock-wise direction. Similarly, the positively charged carriers in the p-type pellet, the holes, absorb heat from the cold side of the couple and transfer this heat to the hot side of the couple in an anti-clockwise direction. Practical thermoelectric modules are manufactured with several of these thermoelectric couples connected electrically in series and thermally in parallel. Arranging the thermoelectric couples in this way allows the heat to be pumped in the same direction.

According to (Rowe, 2006), the energy efficiency of a thermoelectric device, operating in a cooling or refrigeration mode, is measured by its Coefficient of Performance (COP), found by:

$$COP = \frac{\text{Heat absorbed}}{\text{Electrical power input}}$$

(1)

For thermoelectric power generation, if a temperature difference is maintained between two sides of the module, thermal energy is moving through the n-type and p-type pellets. As these pellets are electrically conductive, charge carries are transported by this heat. This movement of heat and charge carriers creates an electrical voltage, called the Seebeck voltage. If a resistive load is connected across the module's output terminals, current will flow in the load and an electrical voltage will be generated. A thermoelectric couple connected as a thermoelectric power generator is shown in Fig. 6.

Fig. 6. A single thermoelectric couple connected as a thermoelectric power generator The efficiency of a thermoelectric module, operating as a power generator, can be found by:

$$\eta = \frac{\text{Energy supplied to the load}}{\text{Heat energy absorbed at the hot junction}}$$

(2)

In thermoelectricity, efficiency is normally expressed as a function of the temperature over which the device is operated, referred to as the dimensionless thermoelectric figure-of-merit ZT.

The thermoelectric figure of merit ZT can be found by:

$$ZT = \frac{\alpha^2 \sigma}{\lambda}$$

(3)

where  $\alpha$  is the Seebeck coefficient,  $\sigma$  is the electrical conductivity, and  $\lambda$  is the total thermal conductivity (Sales, 2007).

Thermoelectric phenomena are exhibited in almost all conducting materials, with the exception of superconductors below specific temperatures. Materials which possess a ZT > 0.5 are usually regarded as thermoelectric materials (Rowe, 2006). The best thermoelectric materials used in commercial macro-thermoelectric devices, Bi<sub>2</sub>Te<sub>3</sub>-Sb<sub>2</sub>Te<sub>3</sub> alloys, operating around room temperature, have typical values of  $\alpha$ =225µV/K,  $\sigma$  = 10<sup>5</sup>/Ωm, and  $\lambda$  = 1.5 W/mK, which results in ZT ≈ 1 (Sales, 2007). Bismuth Telluride is the most common material used in standard thermoelectric modules, as it exhibits the most pronounced thermoelectric effect around room temperature. Other material combinations are also used including; Alloys based on bismuth in combination with antimony, tellurium and selenium; lead telluride; and silicon germanium alloys (Rowe, 2006).

#### 2.5 Development of micro-thermoelectric modules

Standard thermoelectric modules range in size from  $4 \times 4 \times 3 \text{ mm}^3$  to around  $50 \times 50 \times 50 \text{ mm}^3$ . Although, in principle, the dimensions can be reduced further, the fabrication of conventional thermoelectric modules for power generation or heating and cooling applications is a bulk technology, and is incompatible with microelectronic fabrication processes (Volklein & Meier, 2006). The development of micro-thermoelectric devices that are compatible with standard microelectronic technology and manufacturing processes have the potential to enhance the performance of microelectronic systems, achieve significant

reductions in size, improve the performance of thermoelectric devices, and open up new areas of research and commercial application.

Until recently, thermoelectric devices have been confined to niche applications because of their relatively low conversion efficiency and thermoelectric figure-of-merit ZT when compared with other technologies (Riffat & Ma, 2003). For thermoelectric power generation, current thermoelectric efficiencies are between 5% to 10% (Nuwayhid et al, 2005), with a practical thermoelectric figure-of-merit ZT ~ 1. For thermoelectric cooling and refrigeration, a COP of 0.5 is typical, which is lower than that achieved by conventional refrigeration techniques (Bass et al, 2004). According to (Stabler, 2006), since the early 1990's, materials with ZT > 1 have been discovered, and reports of  $ZT \sim 2$  are widely known today with evidence that higher values of ZT are possible (Vining, 2007). Improving the efficiency and thermoelectric figure-of-merit ZT, reducing the cost of thermoelectric devices, and the use of alternative materials that are more widely available are focus areas for current research activity. However, thermoelectric technology does have several advantages over other technologies; For cooling or refrigeration applications, thermoelectric modules do not use any chlorofluorocarbons or other materials that require periodic replenishment; they can achieve precise temperature control to within  $+/- 0.1^{\circ}$ C; the same thermoelectric device can be used for heating or cooling and can cool to temperatures below 0°C (Riffat & Ma, 2003); the modules are electrically quite in operation and are relatively small in size and weight (Alaoui & Salameh, 2001); and do not import dust or any other particles that could cause an electrical short circuit.

## 3. Thermoelectric MEMS devices

#### 3.1 Overview

There is an increasing amount of published research in support of developing MEMS based thermoelectric devices. MEMS technology, combined with microelectronics and micromachining techniques, has been successfully and widely utilised in micro-sensor and micro-actuator applications, and there is significant commercial value in developing next generation thermoelectric devices for applications in power generation and integrated circuit cooling (Huang et al, 2007). Current micro-sensors and micro-actuators may also be based on thermal and thermoelectric principles, and use thin-film technology to achieve sensing and actuator functionality, with micromachining techniques to achieve device optimisation (Volklein & Meier, 2006). According to (Min, 2006), the development of thermoelectric devices compatible with standard semiconductor manufacturing processes has the potential to address many applications in microelectronics, with MEMS technology, along with nanotechnology, of significant interest to thermoelectric manufacturers and researchers. It is anticipated that these technologies can be used to reduce the size, and improve the performance, of thermoelectric devices suitable for micro-power generation, heating and cooling applications. Current MEMS based devices will also benefit from incorporating thermoelectric technology, for example where a MEMS based device has an electrical power consumption in the micro-watt range, this could potentially be supplied by thermoelectric devices (Huesgen et al, 2008), or where there is a need for temperature stabilisation of MEMS based microelectronic components and circuits (Li et al, 2003).

#### 3.2 Emerging thermoelectric MEMS based devices

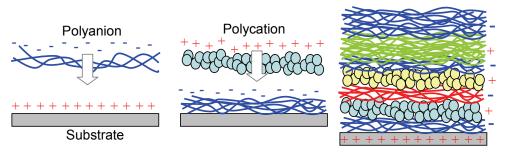

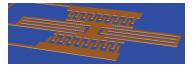

Research into manufacturing a thermoelectric MEMS based device, using thin-film technology, has resulted in the proposal of different device structures; a vertical device

structure; and a horizontal device structure (Min, 2006). Commercially available microthermoelectric devices, based on thin-film technology, have also recently started to emerge. According to (Vining, 2007), two start-up companies have started to market thermoelectric devices based on thin-film technology. One company has developed thermoelectric devices based on a MEMS like process that use a sputtering deposition method and Bi<sub>2</sub>Te<sub>3</sub> related materials. Another company has developed thermoelectric devices based on Bi<sub>2</sub>Te<sub>3</sub>-Sb<sub>2</sub>Te<sub>3</sub> superlattice technology. (Bottner et al, 2007; 2005; 2004; 2002) describe in some detail the development of thin-film MEMS like thermoelectric devices using a sputtering deposition technique. Similarly, (Venkatsubramanian et al, 2007) and (Koester et al, 2006) describe the development of commercial thermoelectric devices using superlattice nanoscale materials.

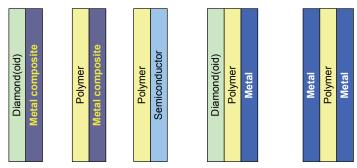

The concept of MEMS like thermoelectric devices for cooling and micro-power generation applications, using a thin-film sputtering deposition technique, is to have a common vertical architecture of thermoelectric devices that use standard silicon/silicondioxide wafers as a substrate. One of these wafers is used to create an n-type semiconductor using Bi<sub>2</sub>Te<sub>3</sub> related materials, and another, separate wafer is used to create a p-type semiconductor. The Bi<sub>2</sub>Te<sub>3</sub> related material is deposited using a sputtering method, and after dry etching to create the device structure, the wafers are then sawn in order to create a single n-type and p-type die. The n-type and p-type die are then soldered together to create a thermoelectric couple (Bottner, 2005).

Another approach to creating micro-thermoelectric devices, that are compatible with modern semiconductor processing techniques, is the development of thin-film thermoelectric devices using nanoscale materials. According to (Venkatsubramanian et al, 2007), significant developments have occurred in the last few years in the area of nanoscale thermoelectric materials using superlattices and self-assembled quantum dots. Thin-film thermoelectric superlattices can be manufactured using Planar semiconductor device technology and are compatible with standard microelectronic processing and packaging tools.

There are a number of other examples of recently published work into MEMS based thermoelectric devices. Although not an exhaustive list, a basic literature search will highlight activity by (Liu et al, 2007) on the integration of micro-thermoelectric devices into a silicon based light-emitting diode (LED) in order to stabilise the LED's temperature; a planar multi-stage micro-thermoelectric device for cooling applications is presented by (Hwang et al, 2008); and the development of two micro-thermoelectric cooling devices, one based on a column-type telluride material, and another using a bridge-type polysilicon material and fabricated using MEMS based techniques by (Huang et al, 2008).

#### 3.3 Future application of MEMS based thermoelectric devices

MEMS based thermoelectric devices can be used in thermoelectric cooling, heating and micro-power generation applications. The miniaturisation of thermoelectric modules, and the potentially higher thermoelectric performance that can be obtained, will also allow the development of new applications to emerge.

Micro-thermoelectric devices, fabricated in thin-film technology, have achieved sufficient miniaturisation to be integrated inside semiconductor packaged devices, rather than having to be mounted onto the outside of a semiconductor device, as is normal with a macro-thermoelectric module. As the semiconductor industry further reduces the size of transistors in integrated circuits, a trend is to fabricate more of the external circuitry inside the semiconductor packaging. Removing the heat within these integrated circuits is becoming

more of a design challenge, and the miniaturisation of cooling devices can be used to solve these problems (Baliga, 2005). Historically, the motivation for using thermoelectric technology to cool microelectronic integrated circuits in the computer industry has been to increase their clock speed below ambient temperatures. Increasing microprocessor performance has usually been accompanied by an increase in power and on-chip power density. Both of these present a challenge in cooling microelectric devices (Mahajan et al, 2006). The computer industry may begin to approach the limit of forced-air cooled systems and will need to find alternative solutions (Sharp et al, 2006).

Localised areas of high heat flux on microprocessors can produce 'hot spots' that limit their reliability and performance, and are becoming more severe as local power density and overall die power consumption increase. Although a macro-thermoelectric module can be used in this application to provide cooling of the entire integrated circuit, micro-thermoelectric cooling of these localised regions of higher temperature or 'hot spots' may provide a better alternative. According to (Snyder et al, 2006), embedded thin-film micro-thermoelectric devices is a promising approach to reduce the temperature of localised, high heat flux hot spots generated by modern microprocessors. Micro-thermoelectric devices are also suitable for addressing other thermal management problems in microelectronics, and could be used to cool or stabilise the temperature of laser diodes, and provide a faster response time than conventional cooling techniques. It may also be possible to integrate a micro-thermoelectric devices (CCD), light-emitting diodes (LED) and other opto-electronic devices may also benefit from micro-thermoelectric cooling.

Thermoelectric micro-power generation and energy harvesting is also a target market for micro-thermoelectric devices. (Bottner et al, 2007) believes that self-powered electronic sensor systems will require MEMS like manufacturing of micro-thermoelectric devices to meet the high volume requirements of this market. Energy harvesting or scavenging systems can be designed to replace batteries in autonomous sensor and wireless systems, and it has been shown that body heat can be used as an energy source to power low-energy devices, including a wrist watch or hearing-aid (Weber at al, 2006). Micro-thermoelectric power generators could also be used to supply power to electronic devices for wearable electronics applications (Bottner, 2002).

# 4. Conclusion

Thermoelectric technology can be used in cooling, heating and micro-power generation applications. Macro-thermoelectric devices have developed significantly since their introduction in the 1960's, and have achieved commercial success in mini-refrigeration, cooling and space-craft power applications. There is a requirement to reduce the size, and improve the performance, of current thermoelectric devices in order to address the need to solve thermal problems in microelectronics, and create localised low-power energy sources for electronic systems.

The miniaturisation and development of MEMS based thermoelectric devices has the potential to improve the performance of thermoelectric devices, and create new applications for the technology. Thermoelectric MEMS based devices, based on thin-film technology, that are compatible with modern semiconductor processing techniques have now started to enter the market place. Thermoelectric devices based on a MEMS like process that use a sputtering deposition method and  $Bi_2Te_3$  related materials, and thermoelectric devices manufactured using  $Bi_2Te_3$ -Sb<sub>2</sub>Te<sub>3</sub> superlattice technology are two recent entries into the thermoelectric market place.

It is anticipated that MEMS based thermoelectric devices can address the need to solve thermal problems in microelectronics, including the cooling of integrated circuits in the computer industry, and the cooling of optoelectronic and telecommunication devices. Micro-thermoelectric power generation is also expected to supply low-level localised power to other electronic components and systems, and provide a power source for energy harvesting systems.

# 5. References

- Alaoui, C.; Salameh, Z.M. (2001). Solid State Heater Cooler: Design and Evaluation, Proceedings LESCOPE, pp. 139-145, 2001

- Baliga, J. (2005). Thermoelectric Cooling Prepares for the Small Stage. *Semiconductor International*, October 2005, pp. 42

- Bass, J.C.; Allen, D.T.; Ghamaty, S.; Elsner, N.B. (2004). New Technology for Thermoelectric Cooling, Proceedings of 20th IEEE Semiconductor Thermal Measurement and Management Symposium, pp. 18-20, ISBN 0-7803-8363-X, March 2004

- Bottner, H.; Nurnus, J.; Schubert, A.; Volkert, F. (2007). New high density micro structured thermogenerators for stand alone sensor systems, *Proceedings of 25th International Conference on Thermoelectrics (ICT2007)*, pp. 306-309, ISBN 978-1-4244-2262-3, Jeju Island, June 2007

- Bottner, H. (2005). Micropelt Miniaturized Thermoelectric Devices: Small Size, High Cooling Power Densities, Short Response Time, Proceedings of 24<sup>th</sup> International Conference on Thermoelectrics (ICT2005), pp. 1-8, ISBN 0-7803-9552-2, June 2005

- Bottner, H.; Nurnus, J.; Gavrikov, A.; Kuhner, G.; Jagle, M.; Kunzel, C.; Eberhard, D.; Plescher, G.; Schubert, A.; Schlereth, K. (2004). New Thermoelectric Components Using Microsystem Technologies. *Journal of Microelectromechanical Systems*, Vol. 13, No. 3, June 2004, pp. 414-420, ISSN 1057-7157

- Bottner, H. (2002). Thermoelectric Micro Devices: Current State, Recent Developments and Future Aspects for Technological Progress and Applications, *Proceedings of 22<sup>nd</sup> International Conference on Thermoelectrics (ICT2002)*, pp. 511-518, ISBN 0-7803-7683-8, August 2002

- Hachiuma, H.; Fukuda, K. (2007). Activities and Future Vision of Komatsu Thermo modules. *Proceedings of ECT2007*, Available: http://ect2007.thermioncompany.com/proc.contents

- Huang, I.; Lin, J.; She, K.; Li, M.; Chen, J.; Kuo, J. (2008). Development of low-cost microthermoelectric coolers utilizing MEMS technology, *Sensors and Actuators A*, Vol. 148, No. 1, November 2008, pp. 176-185

- Huang, I.; Li, M.; Chen, K.; Zeng, G.; She, K. (2007). Design and Fabrication of a Columntype Microthermoelectric Cooler with Bismuth Telluride and Antimony Telluride Pillars by Using Electroplating and MEMS Technology, *Proceedings of 2<sup>nd</sup> IEEE International Conf. on Nano/Micro Engineered and Molecular Systems*, pp. 749-752, ISBN 1-4244-0610-2, Bangkok, Thailand, January 2007

- Huesgen, T.; Woias, P.; Kockmann, N. (2008). Design and fabrication of MEMS thermoelectric generators with high temperature efficiency. *Sensors and Actuators A*, Vol. 145-146, 2008, pp. 423-429

- Hwang, G.S.; Gross, A.J.; Kim, H.; Lee, S.W.; Ghafouri, N.; Huang, B.L.; Lawrence, C.; Uher, C.; Najafi, K.; Kaviany, M. (2008). Micro thermoelectric cooler: Planar multistage. *International Journal of Heat and Mass Transfer*, Vol. 52, No. 7-8, March 2009, pp. 1843-1852

- Koester, D.; Venkatasubramanian, R.; Conner, B.; Snyder, G.J. (2006). Embedded Thermoelectric Coolers For Semiconductor Hot Spot Cooling, *Proceedings* 10<sup>th</sup> *Conference on Thermal and Thermomechanical Phenomena in Electronics Systems*, pp. 491-496, ISBN 0-7803-9524-7, San Diego, CA, June 2006

- Li, J.; Tanaka, S.; Umeki, T.; Sugimoto, S.; Esashi, M.; Watanabe, R. (2003). Microfabrication of thermoelectric materials by silicon molding process, *Sensors and Actuators A*, Vol. 108, No. 1-3, November 2003, pp. 97-102

- Liu, C.K.; Dai, M.; Yu, C.; Kuo, S. (2007). High Efficiency Silicon-based High Power LED Package Integrated with Micro-thermoelectric Device, Proceedings IEEE International Conference Microsystems, Packaging, Assembly and Circuits Technology (IMPACT2007), pp. 29-33, ISBN 978-1-4244-1636-3, Taipei, October 2007

- Mahajan, R. ; Chiu, C. ; Chrysler, G. (2006), Cooling a Microprocessor Chip, *Proceedings of the IEEE*, Vol. 94, No. 8, August 2006, pp. 1476-1486, ISSN 0018-9219

- Min, G. (2006). Thermoelectric Module Design Theories, In: *Thermoelectrics Handbook Macro* to Nano, D.M. Rowe (Ed.), pp. 11-1 – 11-15, CRC Taylor & Francis Group, ISBN 0-8493-2264-2, Boca Raton, Florida

- Nolas, G.S.; Sharp, J.; Goldsmid, H.J. (2001). *Thermoelectrics Basic Principles and New Materials Developments*, Springer-Verlag, ISBN 3-540-41245-X

- Nuwayhid, R.Y.; Shihadeh, A.; Ghaddar, N. (2005). Development and testing of a domestic woodstove thermoelectric generator with natural convection cooling. *Energy Conversion and Management*, Vol. 46, No. 9-10, June 2005, pp. 1631-1643

- Riffat, S.B.; Ma, X. (2003). Thermoelectrics: a review of present and potential applications, *Applied Thermal Engineering*, Vol. 23, No. 8, June 2003, pp. 913-935

- Rowe, D.M. (2006). General Principles and Basic Considerations, In: *Thermoelectrics Handbook* – *Macro to Nano*, D.M. Rowe (Ed.), pp. 1–14, CRC Taylor & Francis Group, ISBN 0-8493-2264-2, Boca Raton, Florida

- Sales, B.C. (2007). Critical overview of Recent Approaches to Improved Thermoelectric Materials, Int. Journal of Applied Ceramic Technology, Vol. 4, No. 4, August 2007, pp. 291-296

- Sharp, J.; Bierschenk, J.; Lyon, Jr. H.B. (2006), Overview of Solid-State Thermoelectric Refrigerators and Possible Applications to On-Chip Thermal Management, *Proceedings of the IEEE*, Vol. 94, No. 8, August 2006, pp. 1602-1612, ISSN 0018-9219

- Snyder, G.J.; Soto, M.; Alley, R.; Koester, D.; Conner, B. (2006). Hot Spot cooling using embedded thermoelectric coolers, *Proceedings 22nd IEEE Semiconductor Thermal Measurement and Management Symposium*, pp. 135-143, ISBN 1-4244-0153-4, Dallas, TX, March 2006

- Stabler, F.R. (2006). Commercialization of Thermoelectric Technology, *Proceedings of Materials Research Society Symposium*, pp. 13-21, 2006

- Venkatasubramanian, R.; Watkins, C.; Stokes, D.; Posthill, J.; Caylor, C. (2007). Energy Harvesting for Electronics with Thermoelectric Devices using Nanoscale Materials, Proceedings IEEE International Electron Devices Meeting (IEDM2007), pp. 367-370, ISBN 978-1-4244-1507-6, Washington DC, December 2007

- Vining, C.B. (2007). ZT ~ 3.5: Fifteen years of progress and things to come. (2007), Proceedings of European Conference on Thermoelectrics (ECT2007), Odessa, Ukraine, September 2007

- Volklein, F.; Meier, A. (2006). Thermoelectric Micromechanical Systems, In: *Thermoelectrics Handbook Macro to Nano*, D.M. Rowe (Ed.), pp. 47-1 47–16, CRC Taylor & Francis Group, ISBN 0-8493-2264-2, Boca Raton, Florida

- Weber, J.; Potje-Kamloth, K.; Haase, F.; Detemple, F.; Volklein, F.; Doll, T. (2006). Coin-sized coiled-up polymer foil thermoelectric power generator for wearable electronics. *Sensors and Actuators A*, Vol. 132, 2006, pp. 325-330

# Micro Power Generation from Micro Fuel Cell Combined with Micro Methanol Reformer

Taegyu Kim Chosun University Republic of Korea

#### 1. Introduction

#### 1.1 Background

Thanks to the breakthroughs in microfabrication technologies, numerous concepts of microsystems including micro aerial vehicles, microbots, and nanosatellites have been proposed. Contrary to ordinary electronic devices, these microsystems perform mechanical work and require the extended operation. As their functions are getting complex and advanced, their energy consumption is also increasing exponentially. In order to activate these microsystems, a high density power source in a small scale is required. However, present portable devices still extract power from existing batteries. The energy density of the current batteries is too low to support these microsystems (Holladay et al., 2004). Therefore, a new micro power source is essential for the successful development of new microsystems.

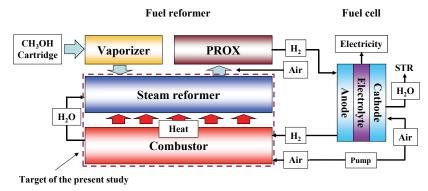

Various concepts for micro power generations have been introduced such as micro engines, micro gas turbines, thermoelectric generators combined with a micro combustor, and micro fuel cells. All of these concepts extract energy from a chemical fuel that have energy density much greater than that of the existing batteries. The first challenge to micro power source was the miniaturization of conventional heat engines. However, the development of micro heat engine reached a deadlock due to the difficulties of microfabrication and realization of miniaturized fast moving components and kinematics' mechanism to generate power in micro scale. Micro fuel cells have drawn attention as a primary candidate for a micro power source due to its distinctive merits that are absence of moving parts and high efficiencies. The fuel cell is an electrochemical device that directly converts chemical energy to electric energy. Due to its different energy conversion path, the fuel cell has high thermal efficiency compared to the heat engines. The energy density of the fuel cell is higher than that of the existing batteries because it uses a chemical fuel such as hydrogen (Nguyen & Chan, 2006).

There are several types of fuel cell as summarized in Table 1 (O'Hayre et al., 2006), such as polymer electrolyte membrane fuel cell (PEMFC), phosphoric acid fuel cell (PAFC), alkaline fuel cell (AFC), molten carbon fuel cell (MCFC), and solid oxide fuel cell (SOFC). Of these fuel cells, PEMFC is suitable to a micro power device due to its low operating temperature and solid phase of electrolyte. Direct methanol fuel cell (DMFC) is a kind of PEMFC except that it directly uses methanol instead of hydrogen as a fuel. Formic acid, chemical hydrides, and other alcohols can be used as a direct fuel.

|                    | PEMFC                               | PAFC                           | AFC            | MCFC                             | SOFC                                  |

|--------------------|-------------------------------------|--------------------------------|----------------|----------------------------------|---------------------------------------|

| Electrolyte        | Polymer                             | H <sub>3</sub> PO <sub>4</sub> | КОН            | Molten<br>carbonate              | Ceramic                               |

| Charge carrier     | H+                                  | H+                             | OH-            | CO32-                            | O <sup>2-</sup>                       |

| Temperature        | 80 °C                               | 200 °C                         | 60-220 °C      | 650 °C                           | 600-1000 °C                           |

| Catalyst           | Platinum                            | Platinum                       | Platinum       | Nickel                           | Perovskite                            |

| Cell components    | Carbon                              | Carbon                         | Carbon         | Stainless                        | Ceramic                               |

| Fuel compatibility | H <sub>2</sub> , CH <sub>3</sub> OH | H <sub>2</sub>                 | H <sub>2</sub> | H <sub>2</sub> , CH <sub>4</sub> | H <sub>2</sub> , CH <sub>4</sub> , CO |

Table 1. Descriptions of major fuel cell types

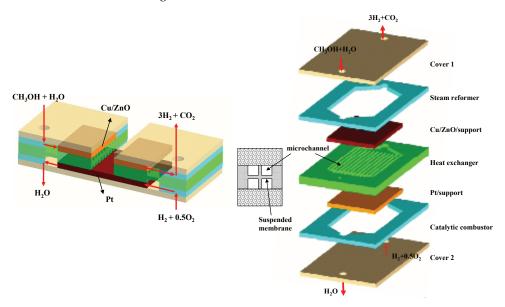

In the beginning of research, DMFC has been widely investigated as a possible candidate for micro power generation due to the use of liquid fuel and its simple structure (Lua et al., 2004). However, the fuel crossover phenomena is an inherent problem of DMFC, which severely limits its power output. It is known that the power output of PEMFC is much greater than that of DMFC, and there is no fuel crossover in PEMFC. Major obstacle in the successful development of PEMFC is the difficulties of the hydrogen storage with high density. Although possible to use hydrogen in either compressed gas or liquid form, it gives significant hazards due to its explosive nature. Metal hydride suffers from high weight per unit hydrogen storage and low response for a sudden increase in hydrogen demand. Chemical storage in the form of liquid fuel such as methanol has significantly higher energy density compared to the suggested technologies. It can be reformed to generate hydrogen gas when needed. The fuel reformer is a device that extract hydrogen from a chemical fuel including methanol, methane, propane, octane, gasoline, diesel, kerosene, and so on. The fuel choice is more flexible than the direct fuel cells. Although a fuel cell combined with the reformer is more attractive, it is complex and bulky compared to the DMFC due to the fuel reformer. Therefore, the miniaturization of the reformer has been a major research activity for the successful development of PEMFC system in recent years (Pattekar & Kothare, 2004). MEMS technology is a useful tool to reduce the size of reformer and fuel cell (Yamazaki, 2004). The use of MEMS technology in a thermo-chemical system is relatively new concept. It allows the miniaturization of conventional reactors while keeping its throughput and yield. The microreactor has a relatively large specific surface area, which provides the increased rate of heat and mass transport, and short response time. In addition, MEMScompatible materials are suitable to various chemical reaction applications due to their high thermal and chemical resistances.

#### 1.2 Literature survey

Catalytic steam reforming of methanol for hydrogen production using conventional reactors has been already carried out in the literature. However, the use of microreactors is a relatively new challenge and other approaches are required for the development of micro reformers using MEMS technologies. Nevertheless, the study on the methanol reforming reaction in the conventional reactors give a good background for the development of micro methanol reformer.

Various research groups have successfully developed micro fuel reformers using MEMS technologies. Pattekar & Kothare, 2004 developed a micro-packed bed microreactor for hydrogen production, which is fabricated by deep reactive ion etching (DRIE). The width of

microchannels was 1000  $\mu$ m and the depth ranged from 200 to 400  $\mu$ m. The microchannels were grooved on 1000  $\mu$ m thick silicon substrate using photolithography followed by DRIE. A 10  $\mu$ m thick photoresist (Shipley 1045, single/dual coat) was used as a etch mask for DRIE. Commercial Cu/ZnO/Al<sub>2</sub>O<sub>3</sub> catalyst was load by passing the water-based suspension of catalyst particles ranging from 50 to 70  $\mu$ m via microchannels. The microfilter was fabricated at the end of microchannels, and the catalyst particles larger than 20  $\mu$ m were trapped in the microchannels. The platinum resistance temperature detector was used as a temperature sensor with a linear temperature versus resistance characteristic. The platinum microheater was deposited along the microchannels. The methanol conversion was 88% at the steam-to-carbon ratio (S/C) of 1.5 and the methanol feed rate of 5 ml/h. The hydrogen production rate was 0.1794 mol/h that is the sufficient flow to generate 9.48 W in a typical PEMFC. Pattekar & Kothare, 2005 also developed a radial flow reactor that has less pressure drop compared to conventional one due to the increased flow cross section area along the reaction path.

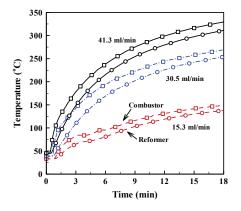

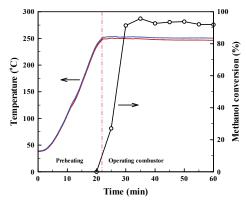

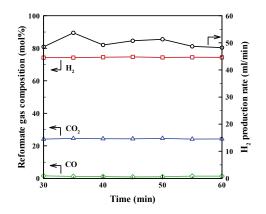

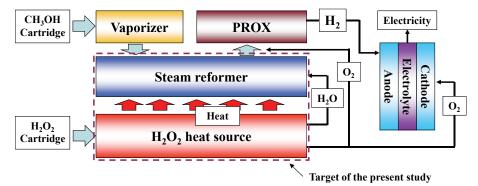

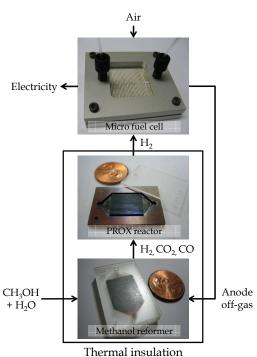

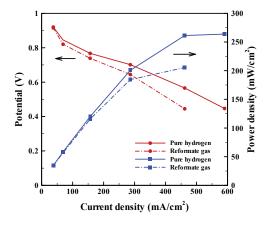

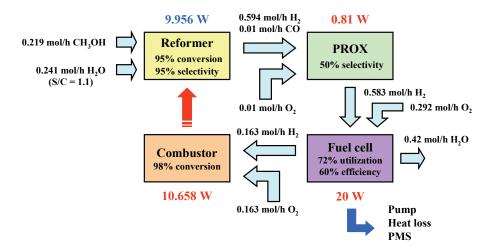

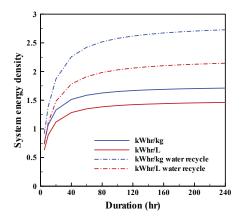

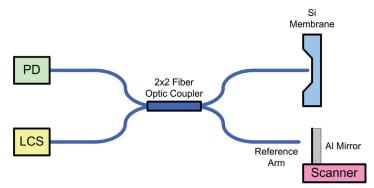

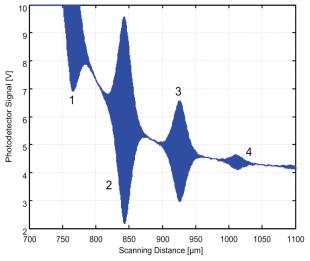

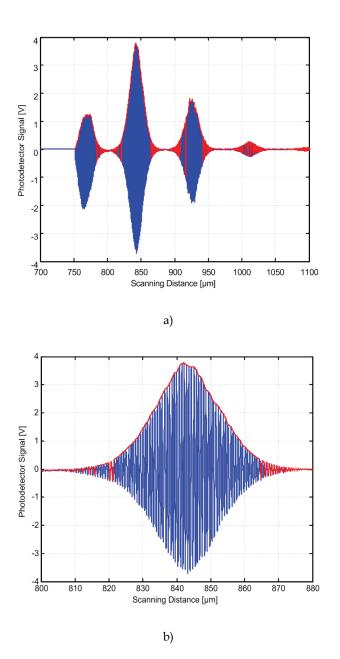

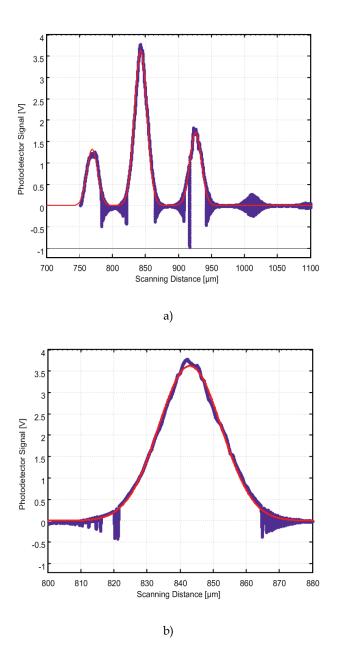

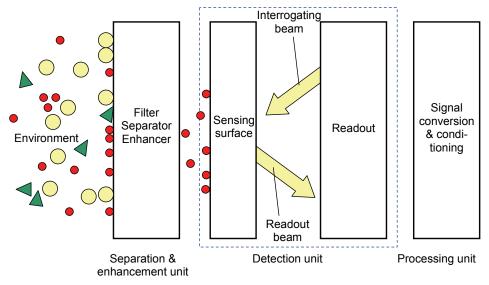

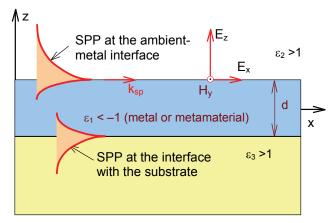

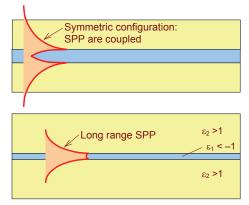

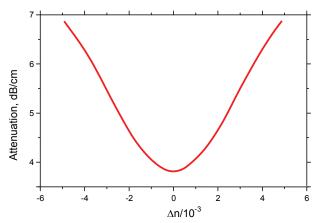

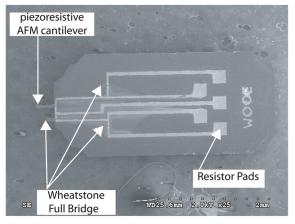

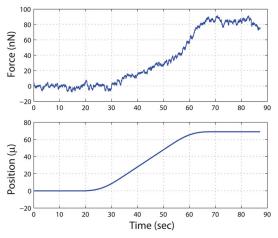

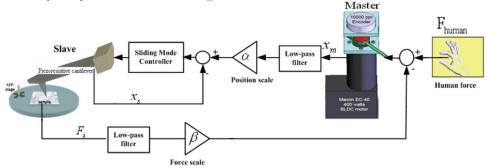

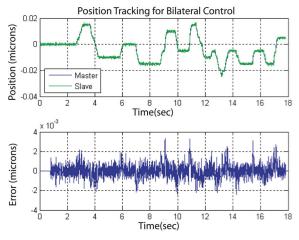

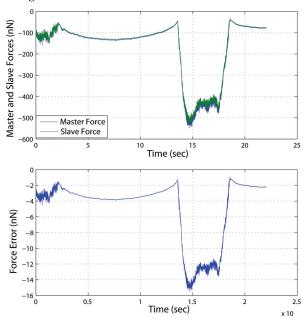

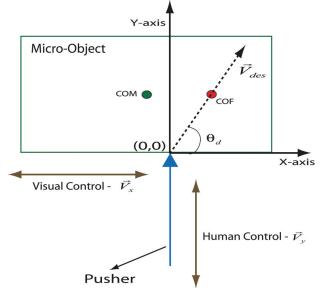

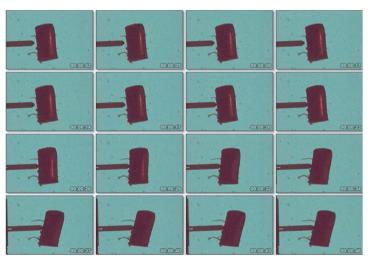

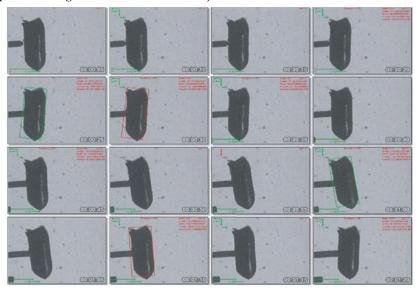

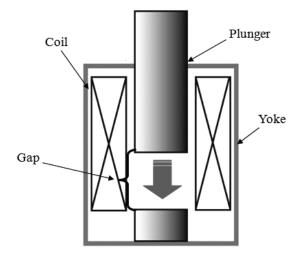

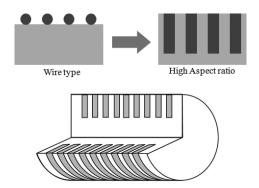

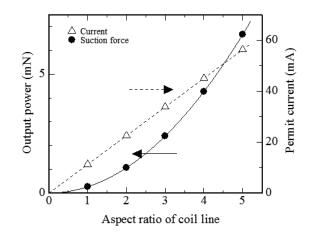

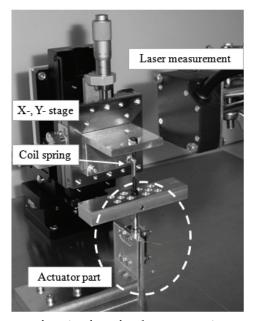

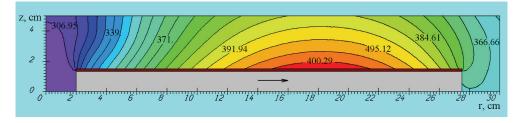

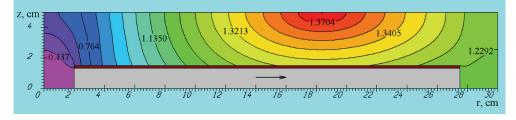

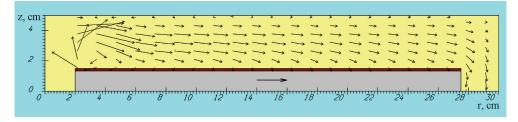

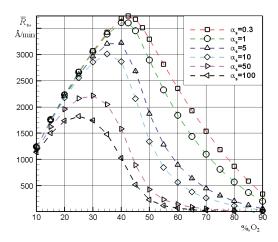

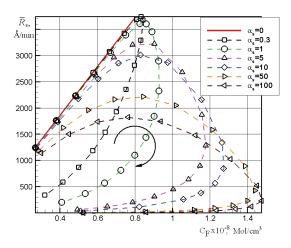

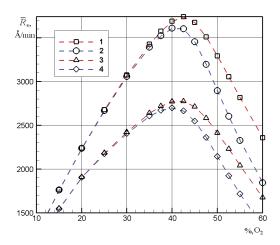

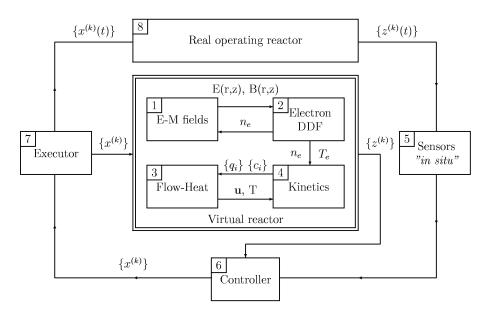

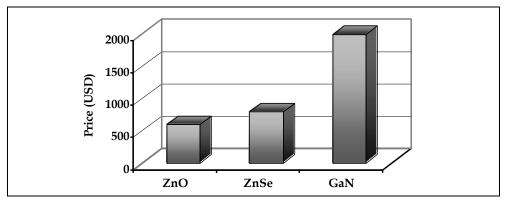

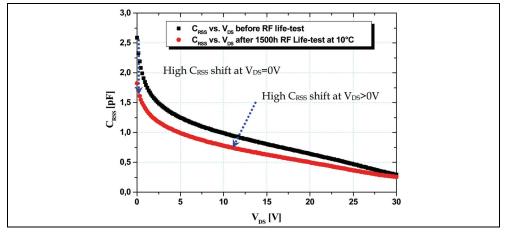

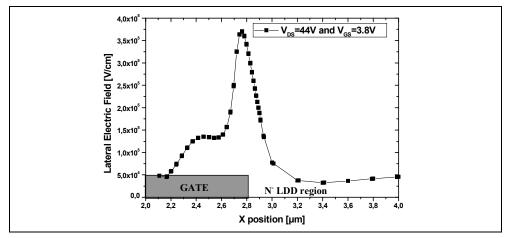

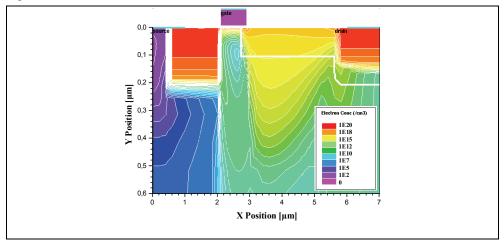

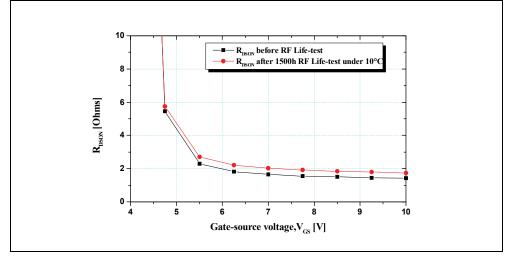

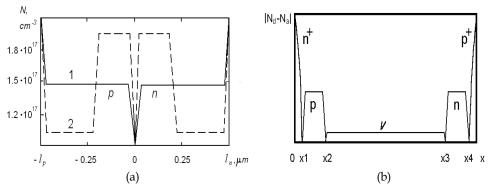

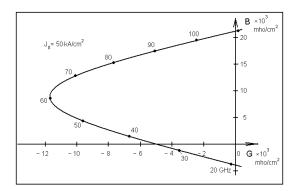

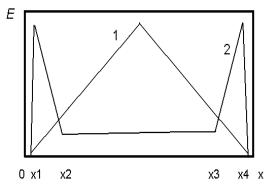

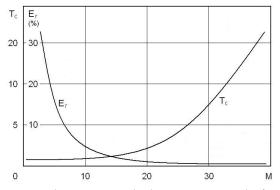

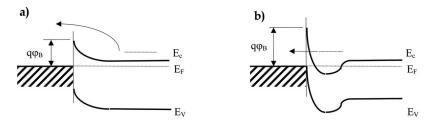

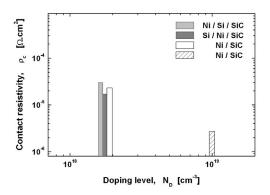

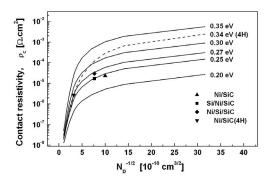

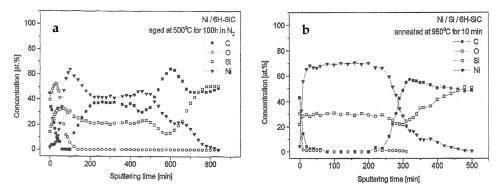

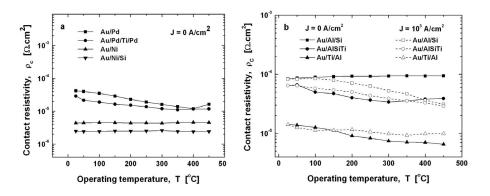

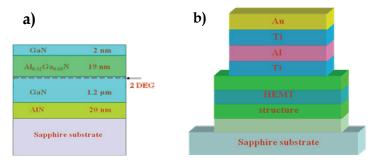

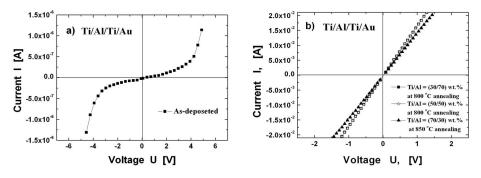

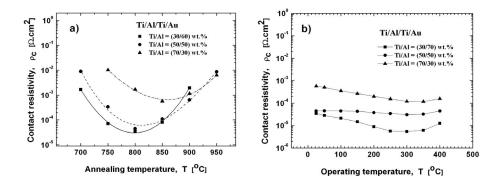

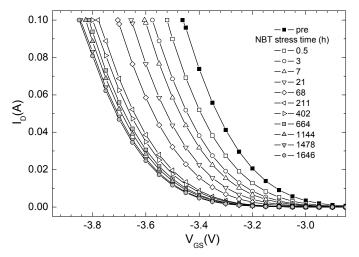

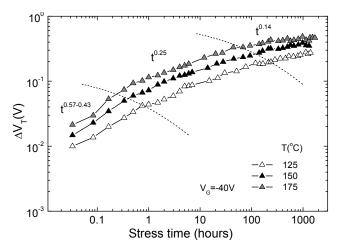

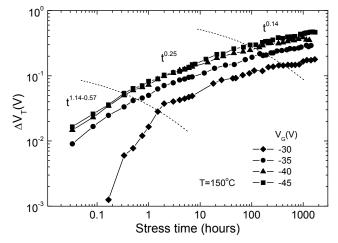

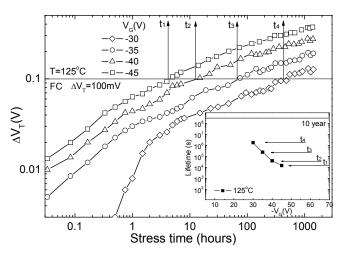

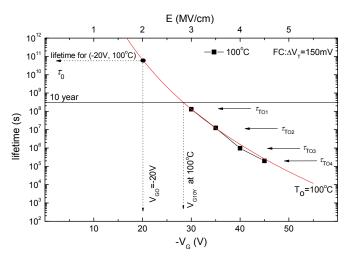

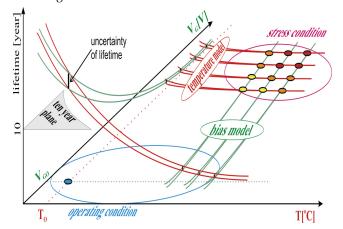

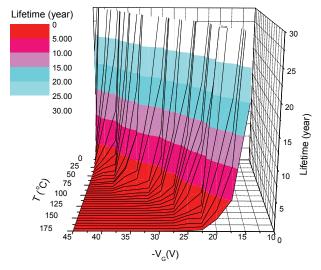

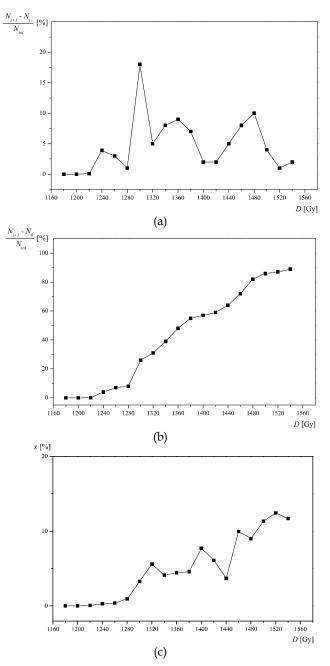

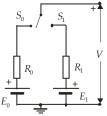

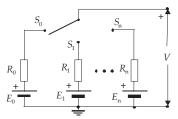

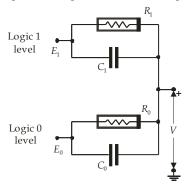

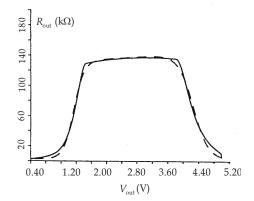

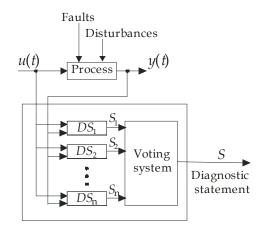

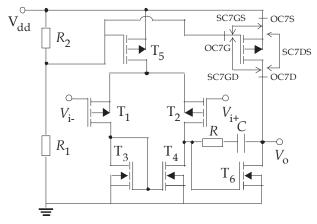

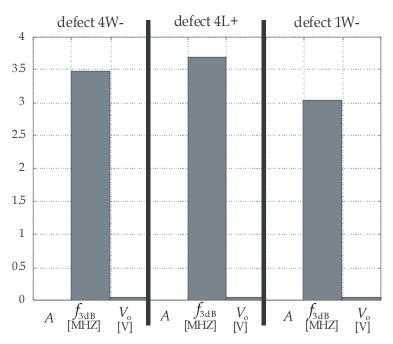

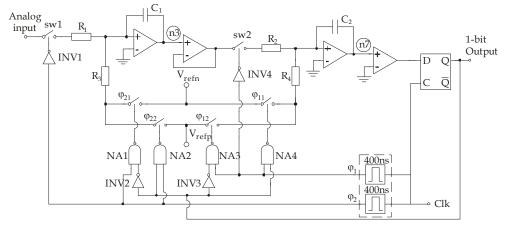

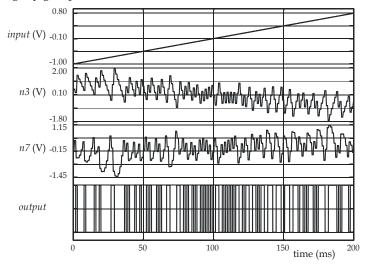

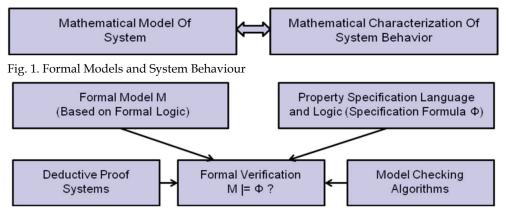

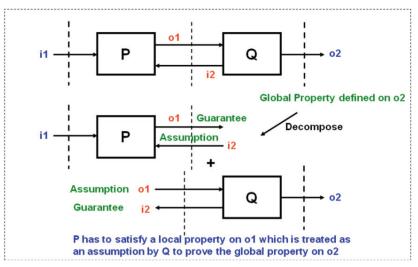

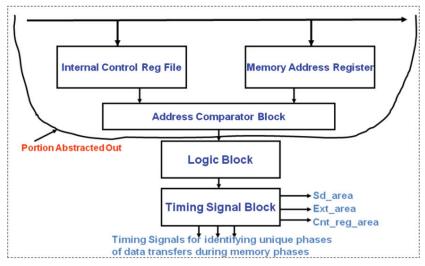

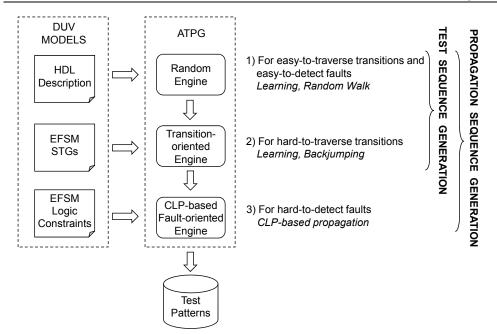

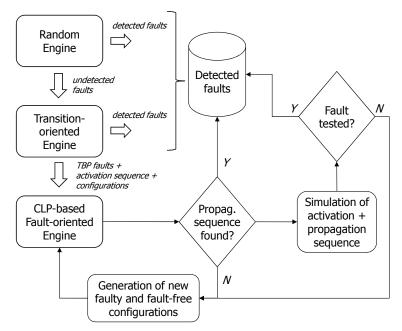

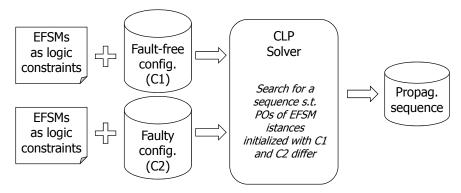

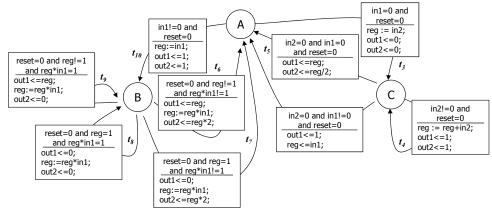

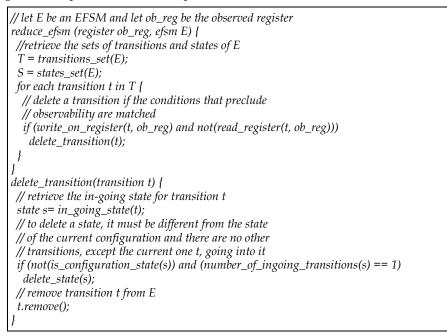

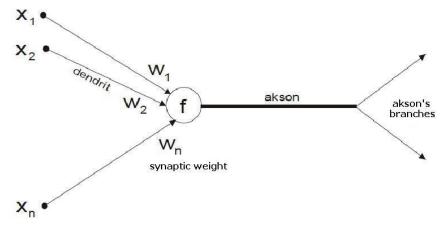

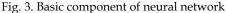

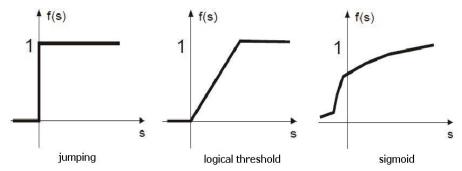

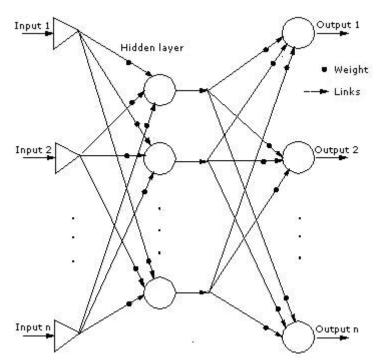

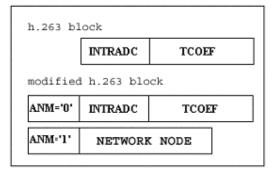

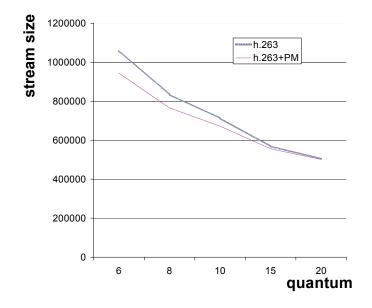

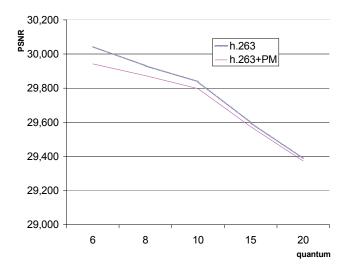

Kundu et al., 2006 fabricated a microchannel reformer on a silicon wafer using silicon DRIE process. The split type channels were made in the micro vaporizer region to reduce the back pressure at the inlet port and to get a more uniform flow of fluid. The dimensions of the micro reformer were 30 mm in length and 30 mm in width, and each channel was 28 mm in length. The width of each channel was 1 mm and the depth was 300  $\mu$ m. The commercial CuO/ZnO/Al<sub>2</sub>O<sub>3</sub> catalyst (Johnson Matthey) was packed inside the channels by injecting the water-based catalyst slurry. The catalyst particles were trapped in the microchannels by filters that were in the form of 90  $\mu$ m thick parallel walls spaced 10  $\mu$ m apart oriented parallel to the direction of the fluid flow. The catalyst deactivation was observed after operating continuously for 8 hours using catalyst characterization. It can be seen that the performance with the serpentine channel was higher than with the parallel channel due to the longer residence time. The hydrogen production rate was 0.0445 mol/h which can produce 2.4 W assuming an 80% fuel cell operation efficiency.